带有实际电容加法器的sigma delta调制器仿真后SNR降低

时间:10-02

整理:3721RD

点击:

请问各位,我目前在做离散时间五阶1.5bits量化的调制器,搭好了verilogA模型,并已经将其中的运放换成了实际的,进行仿真后SNR可达到107dB,但是当把加法器换成实际的电容结构,理想开关换为实际开关以后,SNR就只有60dB了,请问这可能是由于什么原因造成的呢?实际的开关应该不会带来太大的影响吧,难道问题出现在电容上吗?之前的加法器就是用verilog写的一个程序,SNR降低是由于存在直流分量吗,我对这个概念理解的不是很清晰,应该不是频谱泄露的问题吧,我之前仿真的时候用的也是这些参数呀,并没有出现这种问题呀,请各位指教,不胜感激

简单确认一下各个模块的功能是否正确,比如加法器

首先,非常感谢您的回复,我确认了一下,实际的加法器好像并不好使,理想的加法器代码是vout=v1+v2+v3+v4+v5-6,其实对于这个为什么要减去6我也不是很理解,将带有实际加法器的电路仿真后,五个输入电压的总和与输出电压的差值并不是固定的6,而是6点几或者是7左右,我想这应该不是正常的误差范围吧,那就是实际的加法器出了问题,但我是按照别人的论文搭的结构,取值也参考了那篇文献,难道是电容的取值有所偏差才会造成这样的结果吗?期待您的指导

电容加法器是不准的,有开关的寄生电容跟电荷泄漏(如果不是cmos开关的话)。

其实我比较想知道SNR怎么得到的。1.5bit量化跟1bit量化还有多(4)bit量化的代码有啥区别,能不能给个参考的代码。真心谢谢

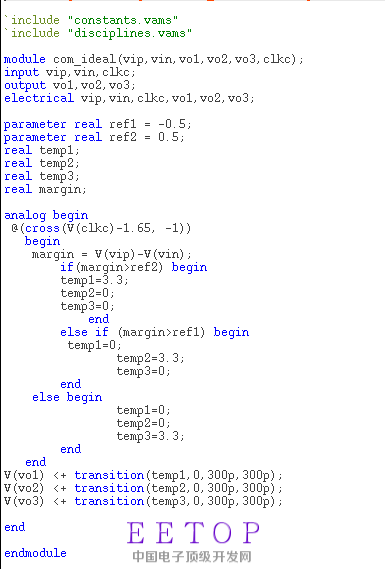

我已经用了CMOS开关,可是结果还是不对呀,你有关于电容加法器的资料吗,我一直也没找到具体的资料,现在也不知道该从哪里改起呀,下面是一个1.5bits量化器的代码,仅供参考

谢谢,开关电容加法器可以使用有源加法器来代替,有源加法器类似于积分器搭建的方法,只是输入端采用开关电容加法器一样的多支路接入。

另外我想知道的是SNR的计算方法0.0,量化器这个我是有做了的,再次表示感谢。