外部磁场对片上LC振荡电路的影响

时间:10-02

整理:3721RD

点击:

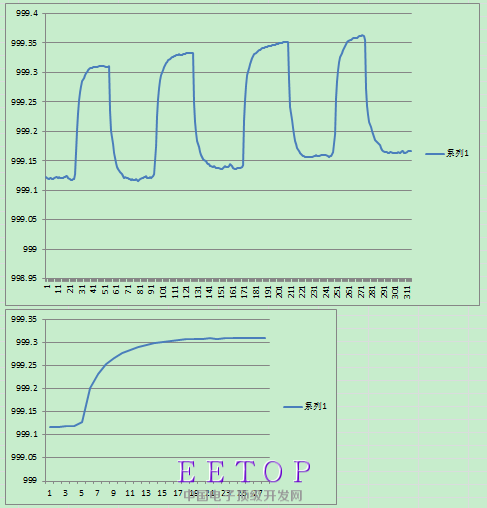

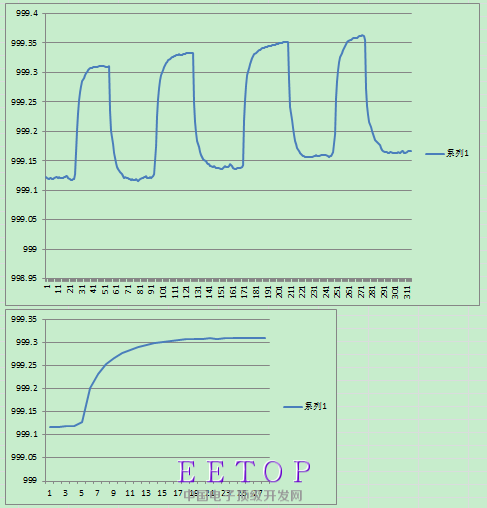

最近做了一些关于LC振荡电路的测试,其中有一个是用一块外部强磁铁放置到芯片表面,观察振荡器输出频率的变化(因为最终芯片要在外部有强磁铁的环境下工作),结果发现了如下图有趣的现象,芯片工作频率接近1GHz。

上图是四次将强磁铁放到芯片表面再拿走的测试结果,下图是第一次磁铁放置到芯片表面的测试结果。

发现当磁铁放置到芯片表面时,工作频率会有一个上升,而且这个频率上升到稳定的斜率并不是很陡,而是比较缓慢(如下图);

此外,每次加磁铁拿走磁铁这个过程会让工作频率整体有一个上升的趋势;

想请教一下大家,有人了解这是什么现象么(我现在的理解是霍尔效应导致的这个现象),但具体为何建立时间这么缓慢(感觉一个电路的建立过程不是应该很快么?)

还想请教一下大家,一个开环的振荡电路上电后,工作频率到什么时候会稳定下来呢?为什么我测试时候发现电路频率一直在抖动中整体漂移,频率很难稳定在一个基线上抖动,想问下大家这是正常现象吗?是什么原因呀(是因为温度变化么)?

非常感谢!

上图是四次将强磁铁放到芯片表面再拿走的测试结果,下图是第一次磁铁放置到芯片表面的测试结果。

发现当磁铁放置到芯片表面时,工作频率会有一个上升,而且这个频率上升到稳定的斜率并不是很陡,而是比较缓慢(如下图);

此外,每次加磁铁拿走磁铁这个过程会让工作频率整体有一个上升的趋势;

想请教一下大家,有人了解这是什么现象么(我现在的理解是霍尔效应导致的这个现象),但具体为何建立时间这么缓慢(感觉一个电路的建立过程不是应该很快么?)

还想请教一下大家,一个开环的振荡电路上电后,工作频率到什么时候会稳定下来呢?为什么我测试时候发现电路频率一直在抖动中整体漂移,频率很难稳定在一个基线上抖动,想问下大家这是正常现象吗?是什么原因呀(是因为温度变化么)?

非常感谢!

不知道你横坐标是秒还是什么

个人意见:

1. 不了解你的电路结构,因此不能排除霍尔效应。另外几个可能原因(假设你是裸片测试):a.磁性材料大多数磁导率都很高,贴近芯片表面后,会影响你片上电感的磁力线分布,电感产生的磁场一部分被磁性材料吸引,导致电感感值降低,你的谐振频率自然升高了。

b.如果你用的磁铁的电导率也很高的话,还会产生两个问题:1.导电材料贴在片上电感上导致的电感线圈间电容的变化。2.导电材料贴近片上电感后产生的感应电流会抵消电感磁场,导致电感感值降低。

可以考虑做三组实验对比一下:a. 用磁导率接近为1的导电材料,如铜和铝,贴在芯片上,观察频率变化。实验室常见的铜胶带就可以。b.用本身没有磁性但是磁导率又很高的材料,常见的就是铁片(先用磁铁吸一下看看能不能吸住),贴在芯片上,观察频率变化。c,你已经做过的强磁体的实验,作为参照。

这三组实验并不能定性给出具体是哪个原因,建议你还是直接把芯片放到那个强磁场环境中。你芯片工作很可能对静态磁场没有那么敏感,只是因为你目前的测试方法本身引入了前面分析的那些干扰因素。

2. 开环电路谐振频率很难稳定,导致漂移的因素很多,所以才需要pll