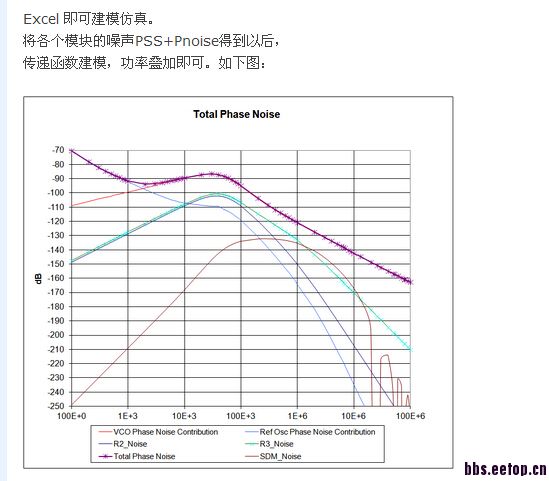

PLL噪声建模

时间:10-02

整理:3721RD

点击:

论坛上有人这样做的,但不知道具体怎么操作的,有介绍相关论文吗,求指导,谢谢!

坐等高手解答

顶一下

我最近也在搞这个,用的是matlab.论坛里有程序。

我有个问题想请教一下,为什么噪声建模的时候,pfd,chp,lpf用的是电压噪声,而reference,vco,divider用的是相位噪声?

PLL环路信号的变换过程而已。VCO是电压积分成相位,divider相位除法,PFD+Charge pume相位转为电压。LPF是电压到电压,或者配合CP 电流到电压。你去看一下环路的各个模块的H(s)表达式就知道了。每个参数的增益单位都不同。反馈系统是控制理论,不是“电压”处理理论。

还有别的更好的答案吗?

十分感谢,之前一直没有关注单位。

能分享给我下吗?我不是很明白 谢谢email:531626519@qq.com

您好,有EXCEL建模文件吗分享一个谢谢