我检查师兄做的电路时发现这个启动电路好像有点问题

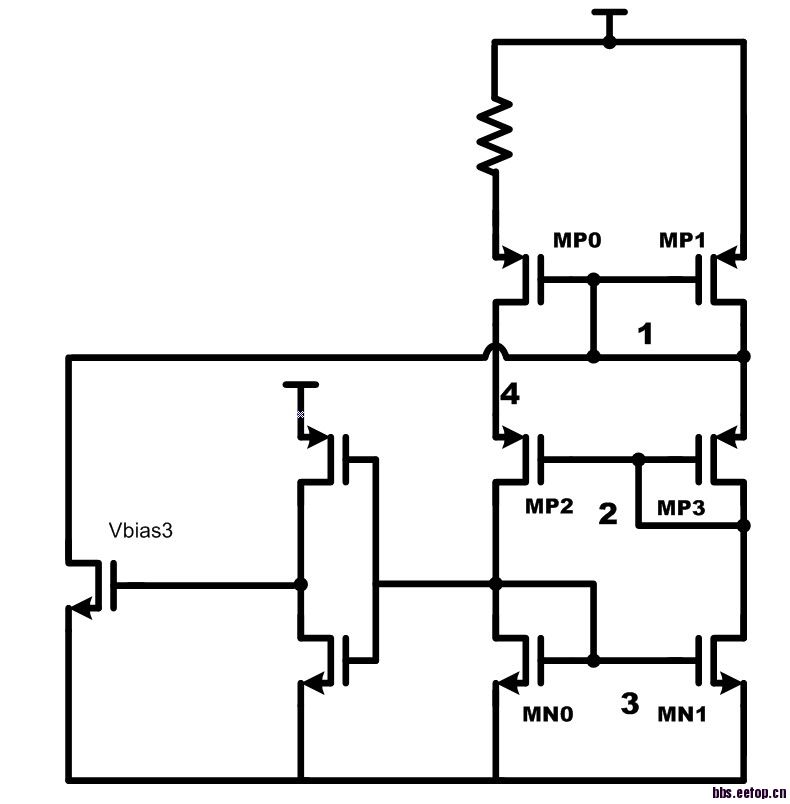

如图所示(因为实验室电脑未联网所以用手机拍照有点糊请大家见谅),一个很简单的电流产生电路,虽然各种仿真都没有问题,但我还是觉得这个电路有点不妥——她存在两个不能启动的非正常的平衡状态:一个是节点123分别为高高低的状态,另外一个是节点123分别为低高低的状态。而启动电路只能够启动第一种情况,不能启动第二种情况。

但是师兄的解释是

1。这两种情况的简并工作点其实是同一个,给它加一个初始的电流激励它就能正常工作;

2。上电过程中,由于PMOS管自身电容的作用,节点2会跟着节点1一起被拉低。

我有点迷糊。请教各位大神,他的解释对吗?如果不对,这个电路该怎么改进呢?

2012-3-27 09:28

你说的第二种情况瞬态可能存在,那种直流工作点是不存在的,即那并不是一个简并点;

假设初态:1为低,2为高,3为低,由于启动电路4为低。MP2因为2高4低导通,MP3因为2高1低会导通,使MN0,MN1就会有电流

学习了

“ MP2因为2高4低导通,MP3因为2高1低会导通” 说不通啊

嗯我想错了 等待高人解答

小编的问题的确是个好问题:

一个是节点123分别为低高低的状态,如果器件可以完全关断的话,从理论上讲确实可能无法启动。

但因为上电的电容耦合以及对节点电容的充电,你所说的低高低很容易被打破。

但如果启动电路顺带2的pmos带上一起启动,你的问题也就解决了。

改动:就是多加一个nmos,d端连接 节点2 即可

同时下拉是个好办法

非常感谢!明白了!

觉得小编的看法是对的,个人犯过类似的错误,在仿真中发现启动时间几百个us,检查下来才发现这个问题,之前一直以为对,怎么也没问题,可怕的惯性思维啊。

我的理解是,启动电路是考虑到电流是零的情况。如果3节点是低,启动电路工作,有额外电流流过中间的diode connected的p管,就会把2节点拉低的,最后使1、2节点相互follow。

初始状态节点3为低,所以节点1被拉低,电流流过电阻和MP0的沟道。通过MP0沟道的电流将不可避免的对MP2的源极节点充电,MP2在电流偏置下是可以建立正常的vgs的。所以低高低的情况也是可以启动的。

建议小编把启动电路的反馈从结点1改接到节电2, 这样应该就能满足小编的需求了。

应该不行的吧。

上下电流源都是截止的状态,拉中间的栅极管用吗?哪一端做电流源?

在电路没有启动的情况下, 拉低结点2, 结点1自然也就低了。

不一定哦. 这个可不是电流偏置的情况,你还没有电流呢. 电流从哪里来?

还是再加一路start比较安全

7楼的回答很好。

学习了, 谢谢

建议你去按照我的方法仿真一下,

我同意你师兄的解释,启动过程中1点电压被拉低,由于MP3栅源电容的耦合,2点的电压也会下降,所以这个结构通过合理的设计,低高低也是可以启动的。

正解,下面的四个管子的drain连在一起才可能存在零点,拉节点1可能启动失败或启动时间过长

小编,我是菜鸟。虽然感觉这个电路不难,但是实际分析起来却不是那么一回事。我主要是对原理不太清楚,望您指教一下。

我的分析:在加载vdd的瞬间,节点1.2.3都应该是低电位,随着vdd升高,mp0、2导通,使3点的电压增加,mn0逐渐开启。但此时3点电位通过反相器后对电路并没有影响。当MN0完全导通,3点电位被拉低。经过反馈,1点的电位继续被拉低(2点的电位我感觉不会改变),所以3点的电位会继续升高,再通过反馈,1点电位上升。但是这个启动器并没有在电路开启后就截止啊?

3点一开始是低电平。

难道节点2为高状态不是因为二极管接法连接节点1么?

理论上低高低确实可能不能启动;但问题是如果节点2为高,肯定需要电荷流动,否则它一开始不可能为高;有电流,就让整个都动起来了,肯定不会维持1/2/3低高低。

但这个电路如果持续开关开,可能会有些异常。

你师兄的结论OK但解释不对

低高低在理论上我认为是有可能不启动的,之所以你没有仿真出来是因为在启动拉低1的时候,2确实会跟着下去,不是因为电容,是因为MP3的body diode,因为你的电路中MP3的bulk端接的不是电源,而是1,也就是说V1被拉到很低,V2最高是V1+Vthp左右,肯定也会下来;

如果你想验证你的猜想,把PMOS的bulk端都接电源,然后2的初始值设为高,并且2和电源之间加一个大点的电容,试试看,能不能稳定在低高低的状态;

至于解决办法,前面有人已经说过了,启动电路拉低1改为拉低2,这个没问题,完全正确可行。注意下拉能力要做强一点就可以。

可以启动,但启动时间估计会长,