全差分运放的噪声疑问

时间:10-02

整理:3721RD

点击:

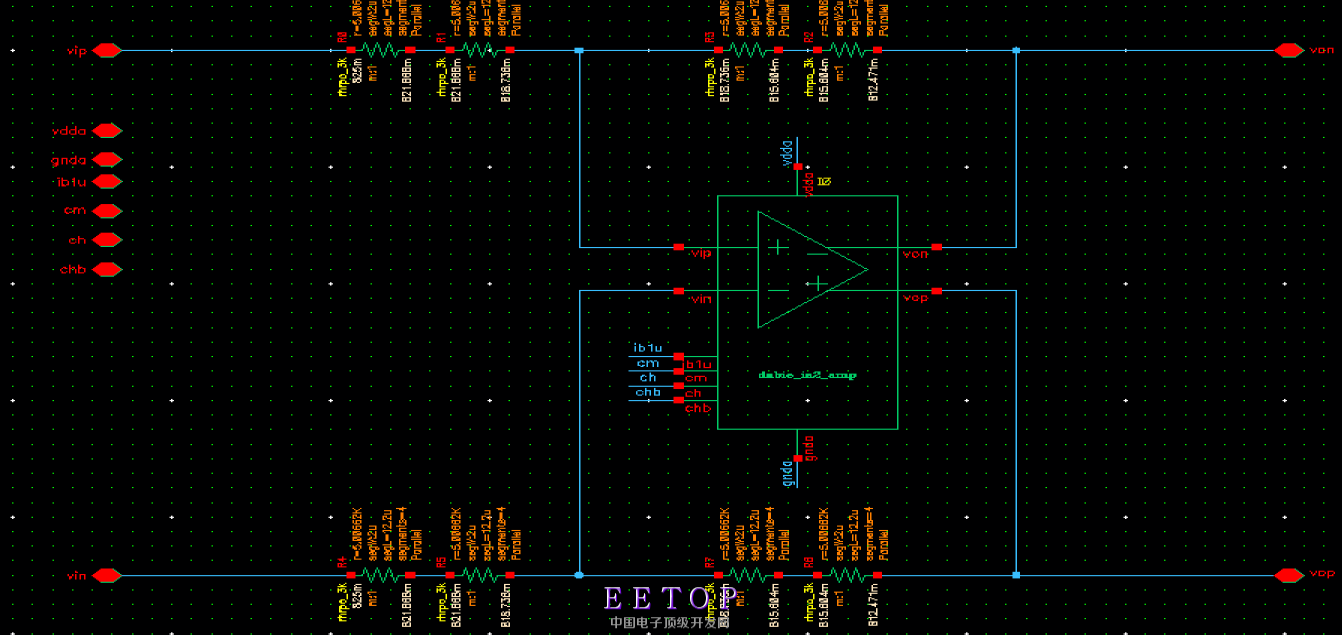

大家好,我现在在设计一个单位增益的全差分运放,如下图所示:

在仿真噪声的过程中出现了一个比较奇怪的问题:单独仿真内部的小运放时,等效输入噪声为350nV^2/Hz(@250KHz和手工计算非常接近),但是加上反馈电阻之后,仿真得到的等效输入噪声不是反馈电阻热噪声和运放噪声的和,并且偏差较大,不知道是什么原因,希望大家指教啊!

我初步怀疑是电阻降低了运放的输出端阻抗,导致运放的开环增益降低,从而使运放的等效输入噪声变大,于是我在预防的输出端加上了VCVS模拟的buffer将电阻和运放的输出端隔开,但是仿真出来的噪声没有变化,不知道大家有没有遇到这种问题,望大家指点啊!:)

在仿真噪声的过程中出现了一个比较奇怪的问题:单独仿真内部的小运放时,等效输入噪声为350nV^2/Hz(@250KHz和手工计算非常接近),但是加上反馈电阻之后,仿真得到的等效输入噪声不是反馈电阻热噪声和运放噪声的和,并且偏差较大,不知道是什么原因,希望大家指教啊!

我初步怀疑是电阻降低了运放的输出端阻抗,导致运放的开环增益降低,从而使运放的等效输入噪声变大,于是我在预防的输出端加上了VCVS模拟的buffer将电阻和运放的输出端隔开,但是仿真出来的噪声没有变化,不知道大家有没有遇到这种问题,望大家指点啊!:)

其中,单仿运放的噪声为350nV^2/Hz(@250KHz),电阻的总噪声为660nV^2/Hz,仿真的总的噪声为2070nV^2/Hz(@250KHz),由于此时运放时接成单位增益,从理论推导上来看,总的噪声应该是运放的噪声加上电阻的噪声为1010nV^2/Hz(@250KHz),不知道为什么仿真会偏差这么大

已解决,是我计算的问题,总的噪声应该是:350*4+660=2060,这样就与仿真的2070对上啦。