求助PLL中VCO设计相关!

时间:10-02

整理:3721RD

点击:

原PLL的capture range是300Hz~8KHz现在要改成900Hz~6KHz改如何设计。

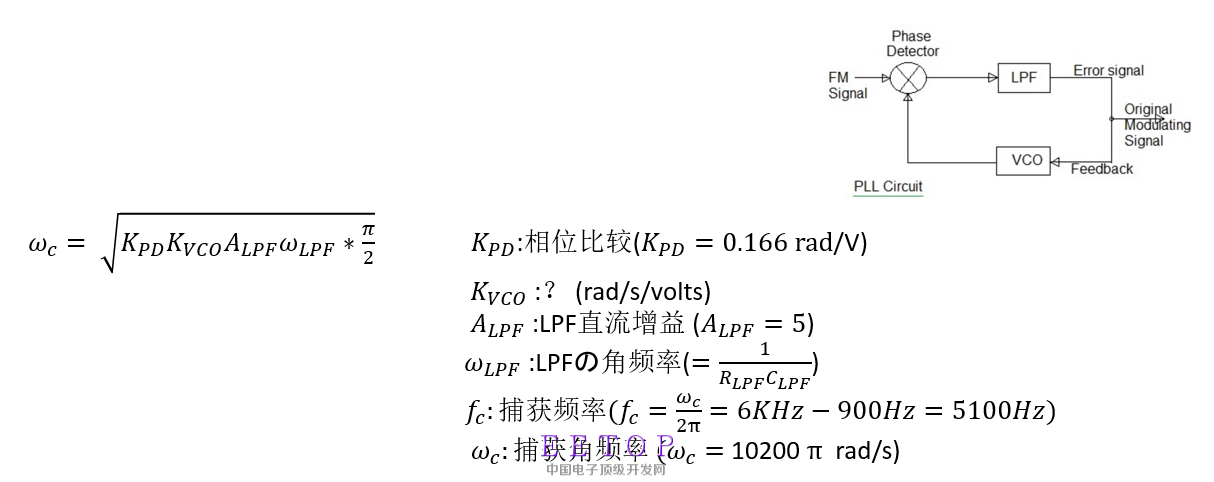

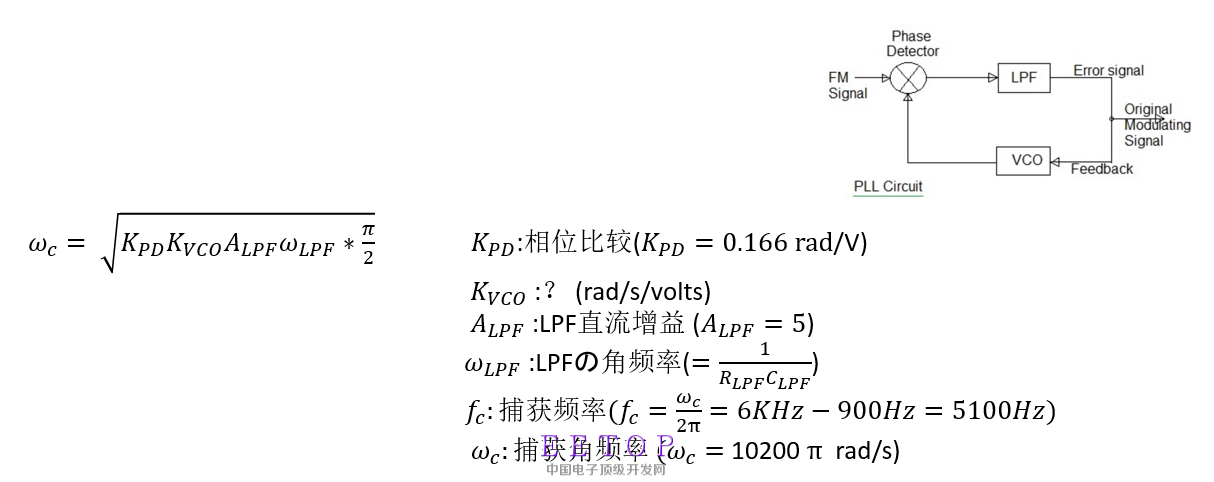

计算公式

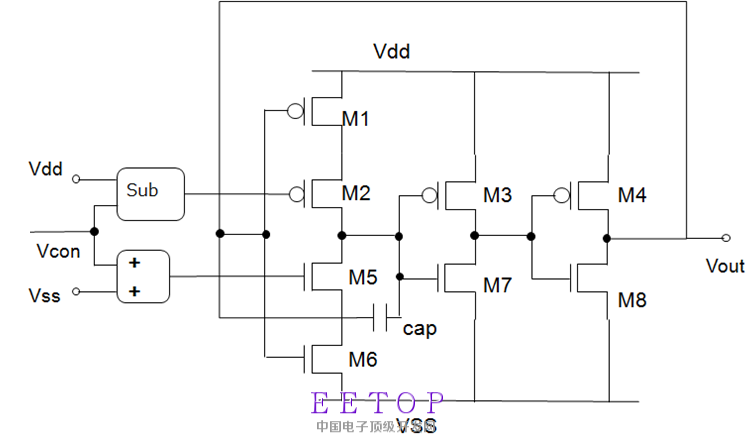

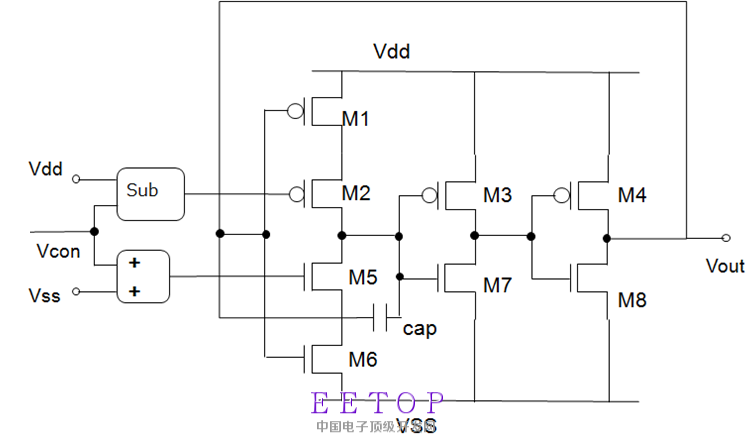

VCO电路图

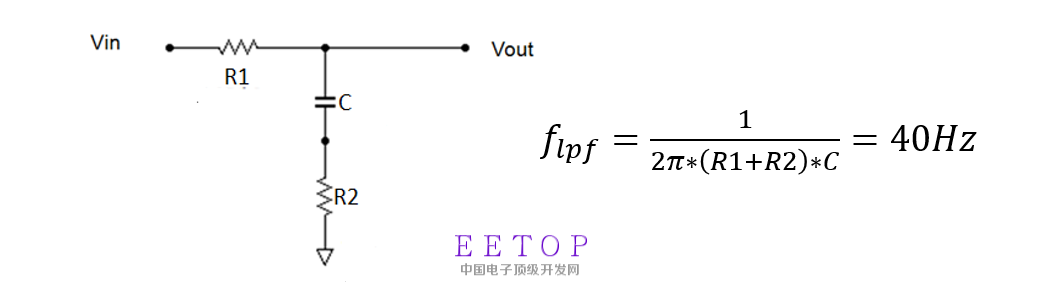

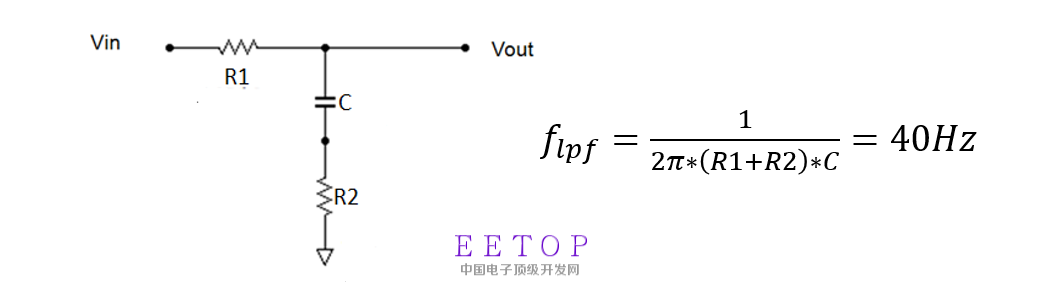

LPF电路图

我把新capture带入计算,得出LPF的截止频率为12.7Hz,然后改了LPF的R,仿真后发现只改LPF并不能实现。请问现在如何改LPF的RC与VCO能够实现900Hz~6KHz的捕获频率?貌似这个公式只能算capture range,但是300Hz~8KHz改成900Hz~6KHz的话,lock的中心频率改变了,应该如何修改来实现呢。好像是修改VCO的M2和M5的W/L,但是具体公式不明,求教。

计算公式

VCO电路图

LPF电路图

我把新capture带入计算,得出LPF的截止频率为12.7Hz,然后改了LPF的R,仿真后发现只改LPF并不能实现。请问现在如何改LPF的RC与VCO能够实现900Hz~6KHz的捕获频率?貌似这个公式只能算capture range,但是300Hz~8KHz改成900Hz~6KHz的话,lock的中心频率改变了,应该如何修改来实现呢。好像是修改VCO的M2和M5的W/L,但是具体公式不明,求教。

这个资料可否发给我看看啊。谢谢!

哪个?公式手打的图是截图,我有讲vco的资料不过是日语的,你要么。

发给我看看啊,这个讲了具体的捕获范围的计算,很是好奇。谢谢啊

没人会嘛

自己顶下

Do you try to change cap value?

mpig

我想通过计算能算出需要修改的值,有什么办法么?

Base on RC time constant, I guess:

1. charge the cap : the R is M1 and M2, cap is cap + cgs,m7

2. discharge the cap : the R is M5 and M6, cap is cap + cgs,m3

I hope this can help you.

mpig