有个貌似很简单的问题搞不懂

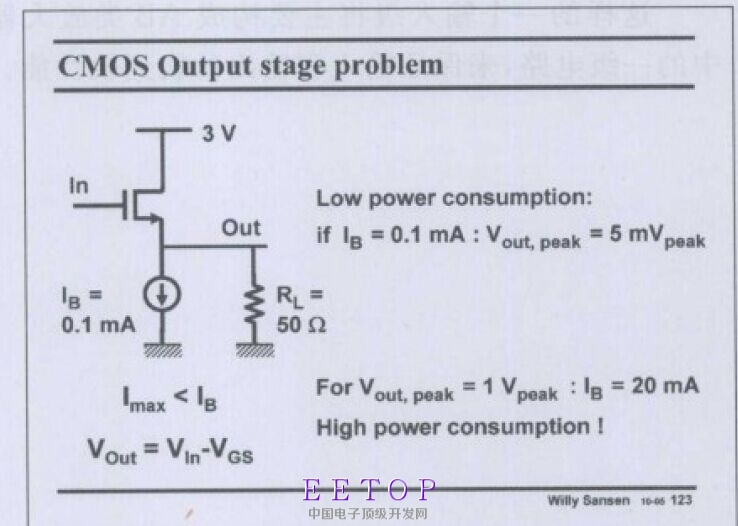

以上图中,电阻下拉电流要小于电流源偏置电流。请问这个是怎么算的呢?多谢啦

不是很懂啊,式子看明白了,没懂想表达什么?

这个电路应该是输出低压时受限制吧,当输出低电压时,Imax小于IB,当输出高电压时,Imax应该可以大于IB吧。忘了sasen咋说的了

我是觉得图画的有点问题,比较难理解。IB想表达的是静态偏置电流,这种画法有点类似小信号电路图(只是把静态偏置电流IB画出来了),平衡时流过电阻的电流为0,Vout为0。然后再Vout跟随Vin期间,由Vout经电阻流向地的电流可以很大,即正向电压可以很大,但是由地经过电阻流向Vout点的电流受静态偏置电流IB限制,所以就是说低压受限制。

在实际电路图中,电流源IB是不存在的,它只是平衡态时流过电阻的电流值而已。

以上是个人看法

还是你理解的透彻。把它当成小信号图,果然好理解。

这个怎么样理解?低压受限?能说的清楚点吗?

图画的不好。IB表示静态偏置的电流,画在图中反而容易引起误解。

首先不是很认同4楼说的Ib不是真是存在的说法。

当IN可以超过VDD时,这个电路的输出最大值可以达到VDD,如果不能超过VDD,那么输出最大值是VDD-VTH,输出电流和IB没有关系,就是VDD/RL,或者是(VDD-VTH)/RL。

输出的最小值是受限制的,即使输入信号能达到很小的值,他的最小值就是-IB*RL+VSS

你们都在讨论什么?

你为啥不把旁边这段话读一读?

这张图的意思就是说,源级跟随器的最大输出电流Imax 是从偏置电流Ib分一部分出去的,如果你把Ib的电流全部拿去驱动Rl了以后vout就直接到地了,所以Imax总是<Ib。

所以源级跟随器的要有大的驱动能力必须要有大的Ib,那样的话静态功耗会非常高。

基于这个原因,所以要采用AB类放大器。

那么问题来了,如果IB为0,那我我的最大输出可以接近VDD,最小为0。只要将平衡时Vout设为VDD/2附近.那么我的输出摆副岂不是接近VDD.。那管IB什么事

那IB为0,就这电路来讲,有驱动能力没有

IB=0.就是说把电流源拿掉,你看看还是源级跟随器么?

怎么不是源极跟随器。如果你担心去掉电流源IB不是源极跟随器,那我的IB假设设得非常小,此电路的最小电压可以到地(假设电流源的驱动电压可以为0),而我最高电压可以为VDD-Vds,那我可以将Vout的平衡电压设为(VDD-Vds)/2,那Vpeak不是可以达到(VDD-Vds)/2。其实这存在一个问题,如果我将Vout平衡电压设为(VDD-Vds)/2,那么流过我的负载RL的电流会非常大,静态功耗会非常高,所以SANSEN这里的IB指的是静态功耗而不是实际的一个电流源。而且你的这句"如果你把Ib的电流全部拿去驱动Rl了以后vout就直接到地了“。既然Vout都接地了,那流过电阻的电流就是0,何来Ib的电流全部拿去驱动Rl了,这和没负载一样,所以你这Ib的电流源到底是拿去驱动Rl没有,是个矛盾。

关于设定VOUT的说法真是呵呵了,请问拿掉电流源以后Vds是多少?你说吧Vout平衡点设定在(VDD-Vds)/2,你想怎么设?你那(VDD-Vds)/2的压降去哪里了?导线上?

基于这副图,我说的是如果ib全部去驱动Rl,那么这边的源级就到地了,确实我这个说法是错误的,因为电流源内阻无穷大,所以vout只和流过RL的电流有关。我在思考的时候把电流源想想成一个mos负载,mos负载并不是恒流源,也就是实际的工作情况,当负载上流过电流为0,就没有压降,所以不可能出现这种情况,这并不矛盾。

首先这个是一个源级跟随器,而不是开关,RL上的摆幅是vin的小信号摆幅,不能影响器件工作于饱和区的状态,所以这个时候VGS是固定的,mos管的漏极电流ID等于IB+流过电阻的静态电流IR。当Vin上叠加小信号,Vin增大带来Vout的增大,IR因此增大,而受VGS确定的ID却不变(一阶模型),因此RL上增加的电流只能从Ib抽,因此IB的大小决定了RL上的电压摆幅。其实考虑2阶模型,VDS因此减小,ID应该会进一步减小。

我说的设定Vout为(VDD-Vds)/2,其中Vds不是平衡时的Vds ,而是我最大的输出电压情况下的Vds,所以并不存在(VDD-Vds)/2跑去哪儿的问题。最大的输出电压时,Vds为多少?这和你管子的宽长有关,这可以将输入电压设为最大得到。平衡时输出电流为(VDD-Vds)/2RL,知道电流和平衡是输出电压,就可以求得平衡时的输入电压。你承认对于实际的电流源你的说法是错的,但对于实际的电流源你的说法也是错的,“实际的工作情况,当负载上流过电流为0,就没有压降,所以不可能出现这种情况,这并不矛盾。”为什么不可能存在这种情况,如果我的输入电压低于预置电压,电路就没电流,那我的输出不是为0?

首先这个是一个源级跟随器,而不是开关,RL上的摆幅是vin的小信号摆幅,不能影响器件工作于饱和区的状态,所以这个时候VGS是固定的,mos管的漏极电流ID等于IB+流过电阻的静态电流IR。当Vin上叠加小信号,Vin增大带来Vout的增大,IR因此增大,而受VGS确定的ID却不变(一阶模型),因此RL上增加的电流只能从Ib抽,因此IB的大小决定了RL上的电压摆幅。其实考虑2阶模型,VDS因此减小,ID应该会进一步减小。

你的语文哪个老师教的,断章取义,我说的是让IB上的所有电流都流到RL上是不可能的。关断是什么鬼?

再问一遍,你知道什么是源级跟随器么?

错洞百出,求输出摆幅当然是考虑极限情况,源跟随器为什么就不能关断。那个老师给你说的源极跟随器的Vgs是固定的,如果这样那源极跟随器岂不是有完美的线性度,那实际上为什么没人用源极跟随器去精确的跟随一个电压。“mos管的漏极电流ID等于IB+流过电阻的静态电流IR“这句话都说了,那我Vgs还是固定的? ”因此RL上增加的电流只能从Ib抽“。为什么从Ib抽取,管子不能提供?你为什么不能把IB当成是整个电路的功耗,是实际不存在的,只是平衡式流过电阻的电流。SANSEN为了考虑,把这个电流拿出来,那么流过电阻的电流为0,相对于平衡时电压,那么输出电压最大只能减少IB*Rl(对于实际情况即使管子关断,Vout为0),但最大的输出电压却可以比这个高,因为管子可以为电阻提供高于IB的电流。所以SANSEN说低压受限,而高压可以更高。再说假设IB是实际的电流源,那怎么去衡量实际的功耗,实际的功耗不光有IB还有流过电阻的电流,这样根本不好衡量。 你不妨带着这种思想在回过去看SANSEN的这段话,你就会懂了。好好想想吧,不要急着反对别人,小编提的这个问题真的很好,你可能还没有弄清问题吧。

再分析把IB拿掉的情况。观察out端的电压,当VIN增大,如果电流增大,RL上的压降会增加,假设VGS不变,VDS也会增大,out端的电压到底增大还是减小?如果VIN减小,能不能确保VDS≥VGS-VTH条件?你怎么不拿笔画一画

关断电压到0就是驱动输出范围可以到0?谁教你的?

对于第一个问题,我不想回答,当输入电压增加时,输出到底增大还是较小,问这问题说明是你对电路工作原理没懂,可以去看书。"如果VIN减小,能不能确保VDS≥VGS-VTH条件",原式即VD>=VG-VTH,VD即电源电压,VG即输入电压,VIN减小,更能保证式子成立。你一直在纠结管子管段问题,那我假设输出一个很小电压Vout0,我输入为一个VGS+Vout0,管子漏电压是VDD大于VGS+Vout0,管子工作在饱和区。上面是把电流源当成理想的,你可能又要说你考虑的是实际的,那我们假设为电流源为实际的管子,像你说的为了保证所有管子工作在饱和区,那么最要的输出电压也应该是有电流源管子的栅极电压确定,而不是管子的电流

首先,什么是大信号,什么是小信号?VGS到底是大信号还是小信号?

第二,你不愿意回答的那个问题,是因为你根本没考虑二阶效应,没想到还有RO这件事。所以你自己也画不出来。

第三,你说的没错,VDS≥VGS-VTH的条件在源级跟随器中是一直满足的,这里应该讨论的是VGS是否还大于VTH的问题,我写错了。

前面还说怎么衡量实际的功耗?怎么不能衡量实际功耗?让VOUT静态在VDD/2,RL不变,IB的增大难道不是功耗的增大?你到底懂不懂模拟?

第一、你如果把VGS当成小信号,那根本求不出输出摆幅,因为增益近似为1,那么输出会跟随输入,输入变化很小,那输出也变化很小,那请问怎么计算输出峰值电压。第二、我并不是回答不上,只是觉得你这个问题根本不是问题,你要愿意听我不嫌麻烦讲一遍。Vin增加,输出电流增加,但VGS不是不变,而是会增大才能通过一个比原来更大的电流。所以Vout并不会完全跟随输入电压,也就是说输出电压会增加,但增加的幅度会比输入的小,VGS增加VDS减小。

第三、就像我前面说的你要担心管子关断,那我假设输出一个很小电压Vout0,我输入为一个VGS+Vout0,管子漏电压是VDD大于VGS+Vout0,管子工作在饱和区。上面是把电流源当成理想的,你可能又要说你考虑的是实际的,那我们假设为电流源为实际的管子,像你说的为了保证所有管子工作在饱和区,那么最大的输出电压也应该是有电流源管子的栅极电压确定,而不是管子的电流。

我承认增加IB会增加功耗,但只是在浪费功耗而已,你要浪费那就没办法了。还有请问你为什么要把Vout偏置在VDD/2。Vout的偏置电压不应该是偏置在最大输出电压和最小输出电压的中间值,这样才能得到最大的Vpeak。既然你都没确定最大和最小的输出电压,你平衡态的输出电压是怎么确定的,你所谓的确定,只是你随便加的一个电压,根本没考虑最后的输出幅度。还有请注意这里计算的是输出电压的峰值,不是摆幅。我咋感觉你不是很懂电路,是不是很久没接触了,感觉像还没入门。随便一个懂电路的人都能看出你的每条回答都有错

首先,什么是大信号,什么是小信号?VGS到底是大信号还是小信号?

第二,你不愿意回答的那个问题,是因为你根本没考虑二阶效应,没想到还有RO这件事。所以你自己也画不出来。

第三,你说的没错,VDS≥VGS-VTH的条件在源级跟随器中是一直满足的,这里应该讨论的是VGS是否还大于VTH的问题。

设置的在VDD/2只是为了举例计算方便,设在摆幅中心不影响最终结论,不要顾左右而言他。

好吧,我终于知道和你交流怎么这么困难,原来你在求输出范围时,还在假设输入为小信号,VGS固定不变。浪费我时间呀,哥哥

好吧,假设你说的都对,那么有两个问题:1. Imax是什么?

2. 下一页上的源级跟随器的IB是否真实存在?

你把RL当作source follower的内部负载,没错,这样的话IB是浪费功耗。那么在没有负载的时候,它和AB类输出级进行对比的意义是什么?如果要考虑RL存在时的静态功耗,那么在平衡位置的AB类输出级静态功耗更低?低在哪?你为了最大的输出摆幅,要把平衡电位设定在(VDD-VDSmin)/2,那么是不是根据不同的负载,你每次都要调整一下管子?

你说IB不是真是存在,好的,我还是那句话,在没有RL的时候,这是个什么东西?

显然Sansen要对比的是source follow和ab class的静态功耗,指的是没有对外驱动电流时的功耗,而此时他们的输入信号和输出信号的电压,以及接负载时最大输出电流能力是一致的。不然,你那个源级悬空的管子根本就是0功耗,AB class毫无优势,那还讲个锤子?

那你说下第三张图中电流曲线代表什么吧,也解释下为什么IB>Imax吧,正如前面我所说,IB我可以去很小也没什么影响。还有源极跟随器不是万能,不是什么负载都能驱动,当然要根据实际负载调节我的管子。在设计电路前负载是什么都不知道,那我不知道你要怎么设计。

看了下格雷的,觉得SANSEN这图有问题。格雷的是双电源,负载接的地,Vout平衡点就为0,流过电阻的电流为了0,这样才能理解。

显然负载的阻抗会是一个范围而不会是单个值,特别是对于音频系统,16欧50欧100欧的都有。本身驱动的设计所关注的点就是电流而不是电压。你说的是对的,另一端应该是平衡点,而不能粗暴的画成地。这也让我的理解出现了偏差。谢谢指出。

学习了

MARK.

搞不懂 相关文章: