怎么降低ADC的FFT仿真结果中的奇次谐波

时间:10-02

整理:3721RD

点击:

各位大大,想问一下为什么ADC的FFT仿真结果中奇次谐波会这么高?尝试将奇次谐波降低,但是会导致底板噪声增加,有没有什么办法将可以只消除奇次谐波

我的是全差分的基于VCO的结构,偶次谐波可以消除,但是奇次谐波总是很大。

我的是全差分的基于VCO的结构,偶次谐波可以消除,但是奇次谐波总是很大。

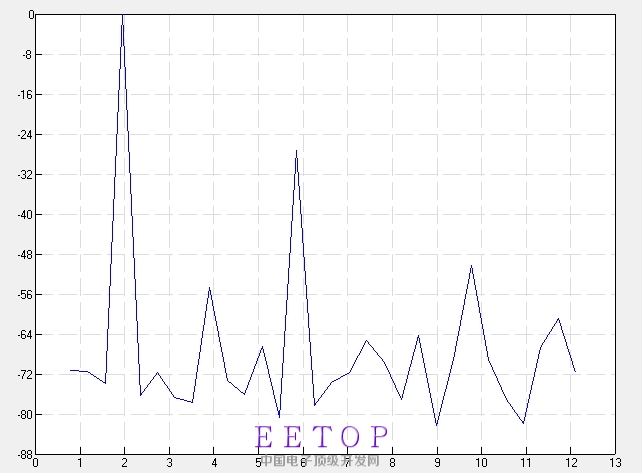

FFT仿真结果,64个点

具体是什么结构? VCO 的 transfer curve 本来就具有很大的非线性,当然,输入幅度越小,非线性就越小,代价就是SNR下降。一般都放在一个sigma-delta loop 里面来解决吧?

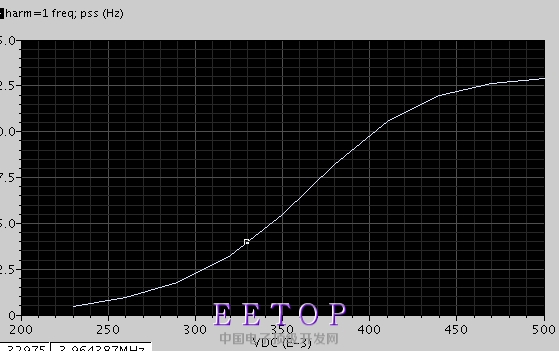

用的反相器构成的环形VCO结构,加计数器,我只选择了很小的一段范围(20mV左右),transfer curve在这个范围内是足够线性的,我现在不想放在d-s ADC中,只想单独利用VCO结构,有没有什么办法呢?

能不能把 transfer curve 或者 INL 发上来看一下。

过载了

INL我还没有仿过,我想让SNDR和ENOB达到想要的结果之后再仿真INL和DNL还有我的 transfer curve,我选择的是中间比较线性的部分,还有我的VCO结构

您好,能帮忙详细说一下吗?谢谢您了

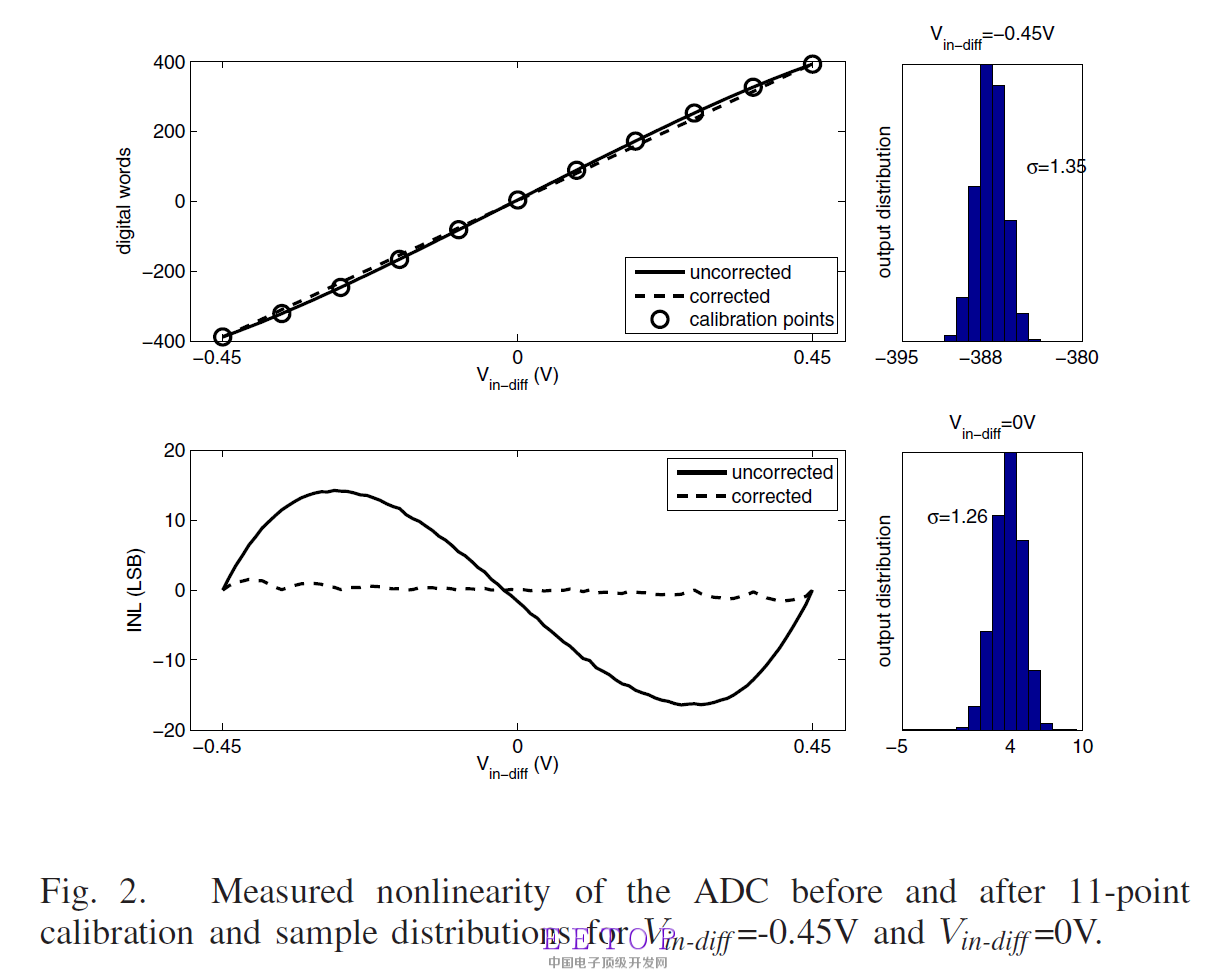

从你的 transfer curve 上来看,即使是中间部分线性度依然很可能比较差,FFT显示线性度只能达到大概四位。你可以把中间用到的那段取出来,然后detrend 一下就可以大致看到 INL 的形状了。这是一篇paper里截的图(A 0.02mm2 65nm CMOS 30MHz BW All-Digital Differential VCO-based ADC with 64dB SNDR, 2010 VLSI):

左上图是 transfer curve,左下图是INL, 实线是原始数据。你可以看到,即使 transfer curve 看上去很线性, INL 依旧很大。

另外, VCO有多种实现形式,你可以在调研一下哪种线性度比较好。PLEASE

好的,非常感谢您的回答,谢谢!