共源级cmos放大器中的电压摆幅是什么

时间:10-02

整理:3721RD

点击:

拉扎维《模拟cmos集成电路设计》中,P48提到输出电压的摆幅

哪位高手解释下,这里的输出电压摆幅为什么会减小。

哪些因素影响输出电压摆幅?

这里的亚阈值电导为什么会使输出接近VDD-Vth呢

哪位高手解释下,这里的输出电压摆幅为什么会减小。

哪些因素影响输出电压摆幅?

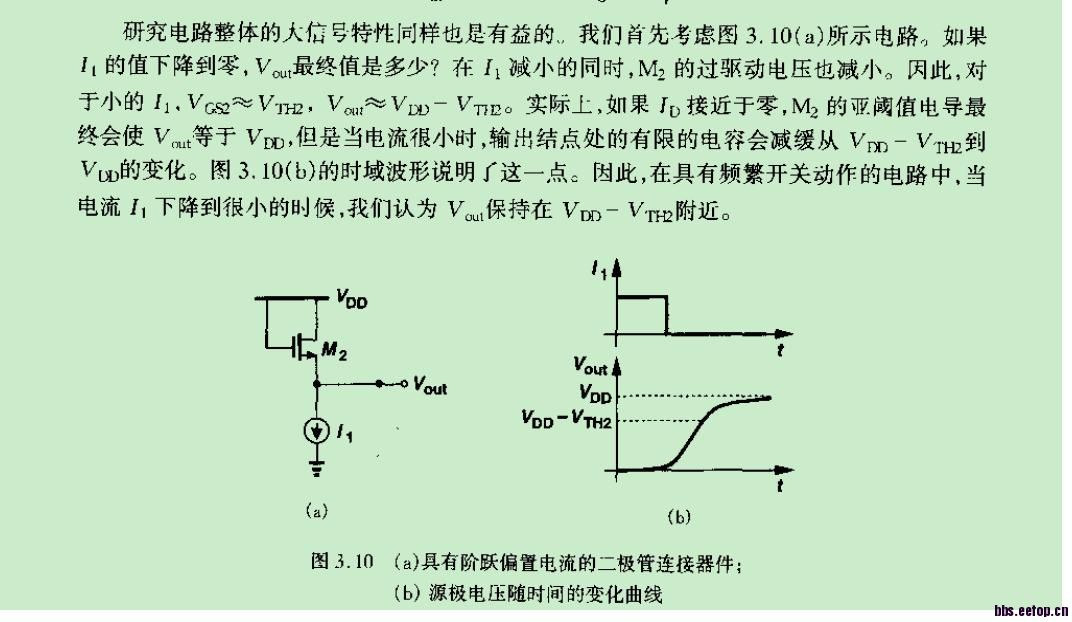

此处的输出电压摆幅变小是因为最大的输出值为Vdd-Vth。如果不是二极管连接的管子,那样最大的输出值可以是Vdd-Vds。

仅仅考虑二极管连接这一种情况的话,为什么高的增益会限制输出电压的摆幅呢

这里的亚阈值电导为什么会使输出接近VDD-Vth呢

当I1减小时,vgs2-vth2也减小,当I1为0时,vgs2-vth2约等于0,所以输出就等于VDD-Vth

我现在的理解程度是单从公式推导可以理解,

但是一和管子联系到一块就有点难以理解了

从管子或者说器件的角度怎么理解这个问题呢

放眼望去,教科书讨论都是Razavi~

我的分析是,书上高增益的意思是大大增大M1的尺寸,就意味着这个M1电流大大增大,而相同的M2,为迎合更大的电流,只能增大VDS,导致最大输出电压输出减小。

如有错误请指正。

是啊。3本经典书籍之一

你是不是已经研究透了?

这个地方增益越大,要求p管的过驱动电压比n管的大Av(增益)的倍数啊,这样VDD-VTH的值就会被拉下,必然减小了电压上限。我看了你在论坛上的一些帖子,疑问在初学都会有很多,不错

呵呵~谢谢啊,努力学习ing。

终于搞懂了,希望这次能记住分析的方法,以前貌似看到过图片的内容,很有帮助