相位90度的时钟怎么产生?

二分频?延迟?

大侠指导啊!

用二倍频率的clk二分频就好了,你搜一下二分频电路,很简单的

normally DLL with taps or div by 2.

depends on your application

1. DLL with pi/4 delay

2. 2 times frequency clock then /2 divider

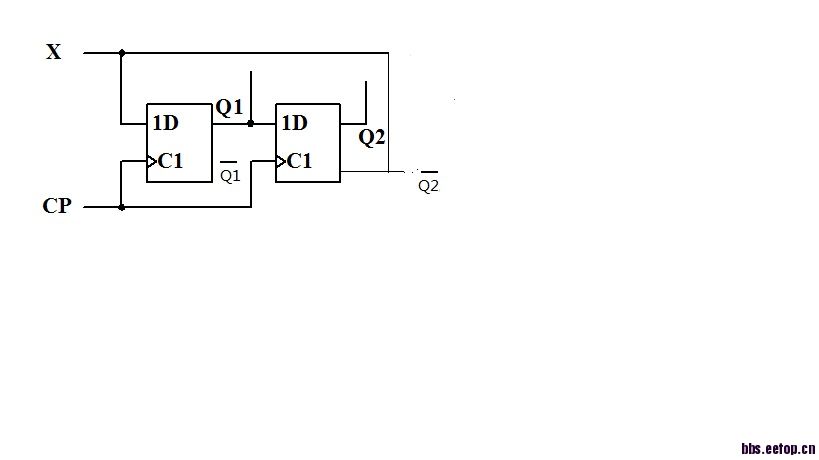

四相时钟发生电路两个同步的D触发器激励函数为D2=Q1D1=Q1的反然后分别从两个触发器的Q1 Q1反Q2 Q2反 提取四个输出信号就可以得到四个相位分别相差90的信号

当然 如果考虑触发器和导线的延时会有所偏差

这个是一种简单方法 我只是一个刚毕业的本科生暂时只会这种方法

如果用2分频电路看似可以其实不然

因为信号的频率被改变了

产生的信号是倍频的不符合你给出的波形而且在每个位置信号相位都相差90只在信号上升沿或者下降沿相差90中间并不同在低频信号的一个周期内倍频信号已经经过了2个周期

你自己可以画divider的波形图看看

另DLL(延迟锁相环)是可以的RF的东西暂时没有学只是大概看了下DLL的介绍原理上是可以的

两种方法各有优缺点choose onedeponds on your application

呵呵,能画一下这个电路图吗?或者至少画几个波形?

如果我没有理解错的话,输入时钟只有一个,90°相移,时钟频率不能改变,那就需要在该时钟的高电平或低电平的中间(一半时间时)产生跳变信号,而如果只用触发器等数字单元,是不可能在高电平或低电平的中间(一半时间时)产生出信号的。

输入时钟是只有一个因为是同步的

其次我所说的相位差90‘的信号是指输出四个信号之间互相差90’这四个信号频率是相同的只不过相位不同所以可以在四个输出信号中取相邻的两个作为新的相差90的时钟!而不是与原时钟CP相差90另:画出输出波形图即可知输出四个信号和原CP的频率和相位关系

能给一些资料吗,谢谢

真是刚想问这个问题,这个问题就来了,同问,我现在就想知道用DLL怎么检测出第二个信号刚好延迟了90度

我想请教一下这个是IQ时钟电路吗