如何分析这个电阻型DAC?

时间:10-02

整理:3721RD

点击:

求大家帮忙分析一下如下图所示的DAC吧,这个电路跟allen写的《CMOS模拟集成电路设计》讲的不太一样,自己推导不出公式:

每一个电流源接入的节点等效电阻都是2/3R

输出端电压是每个电流源连接点的2^n的分压(b0~b6),

b7开始电阻梯结构变了,没有分压,但是电流源开始按照2^n

b0的电流源似乎不对,不应该是2*I0,应该是I0

切记每个电流单独推导,再进行叠加,这是线性系统

这个DAC的优点是current source 和resistor ladder相互分担了2^0~2^9 的权重

如果只用current source,那电流镜跨度太大,b0:b9=1:512,匹配也不容易做好

这种结构就是速度慢了点

您好fuyibin,您说的是对的,b0对应的时I0,不是2*I0

不过您的解释我还是不太明白,您有什么资料提供一下吗?谢谢!

没有资料,我就是看了你画的结构,自己动手算了一下

这是个R-2R ladder,就是电阻并联-串联网络,中间任何一个节点,

向左看等效电阻是2R,向右看等效电阻也是2R,再加上到地的2R,就是3个2R并联

建议你还是耐心的算一算,其实非常简单

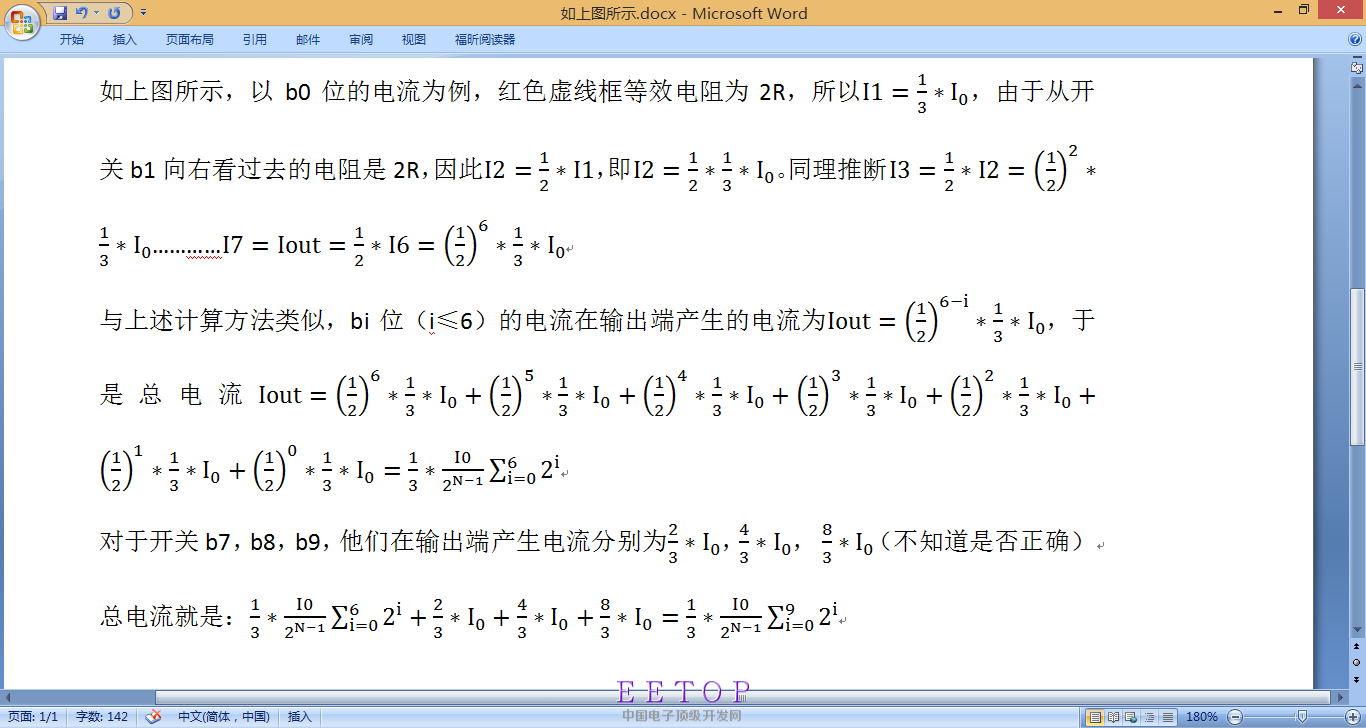

根据fuyibin的提示,自己推导了一下公式,不知道正确与否,还希望大家指点一下:

感觉还是不对,请看下图的公式4-9,书名叫做《CMOS DATA CONVERTERS FOR COMMUNICATIONS》。我的计算结果好像多了一个1/3