PLL使用XOR作为鉴相器后无法锁定

所以想要请教一下以XOR为鉴相器的架构锁频范围如何确定的?为何实际电路无法锁定,该如何修改?

希望各位大虾不吝赐教

顶一下

怎么分析啊?

架构图都没有

不清楚你这个xor是个什么样的,如果只是一个异或门,首先不知道你目标频率是多少,xor可能会锁定到目标频率的谐波上去,另外xor pd对输入信号占空比比较敏感,可能需要对参考和反馈信号做一次二分频保证有50%占空比。

多谢指点,目标频率大约3G,simulink仿真低于2.5G就会无法锁定,所以感觉并不是锁定在谐波频率上,不知道怎么修改。

而且cadence里实际电路搭出来我初始频率给多少都没法锁定

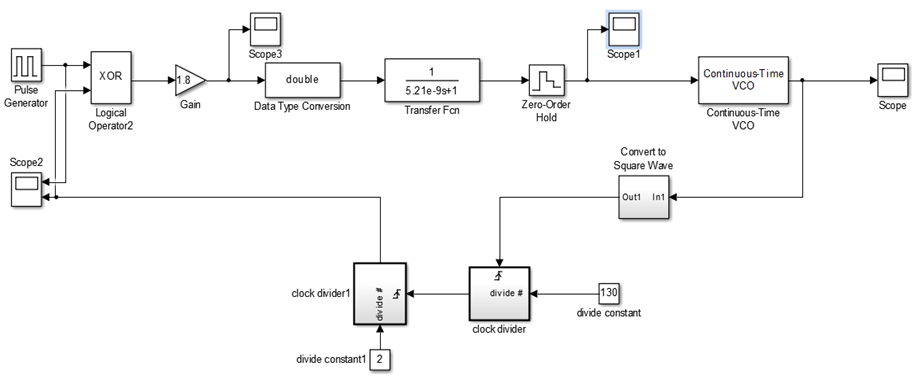

我贴上simulink的model,麻烦帮我看一下鉴频范围怎么提升~

这个属于I型pll,频率捕获范围有限,怎么推导我不知道,基本没见过有用这种类型的架构。

贴一段《射频微电子》上的评论

Second, the simple PLL suffers from a limited “acquisition range,” e.g., if the VCO

frequency and the input frequency are very different at the startup, the loop may never

“acquire” lock. 2 Without delving into the process of lock acquisition, we wish to avoid this

issue completely so that the PLL always locks.

很简单,lpf那边加个积分器,改成II型的。

顶两下

多谢,这个确实是一类PLL,锁定范围有限,目前simulink的锁定范围也可以接受,但是在cadence里就不行了,完全锁定不了

贴个电路图和每个节点波形吧对着空气怎么讨论呢

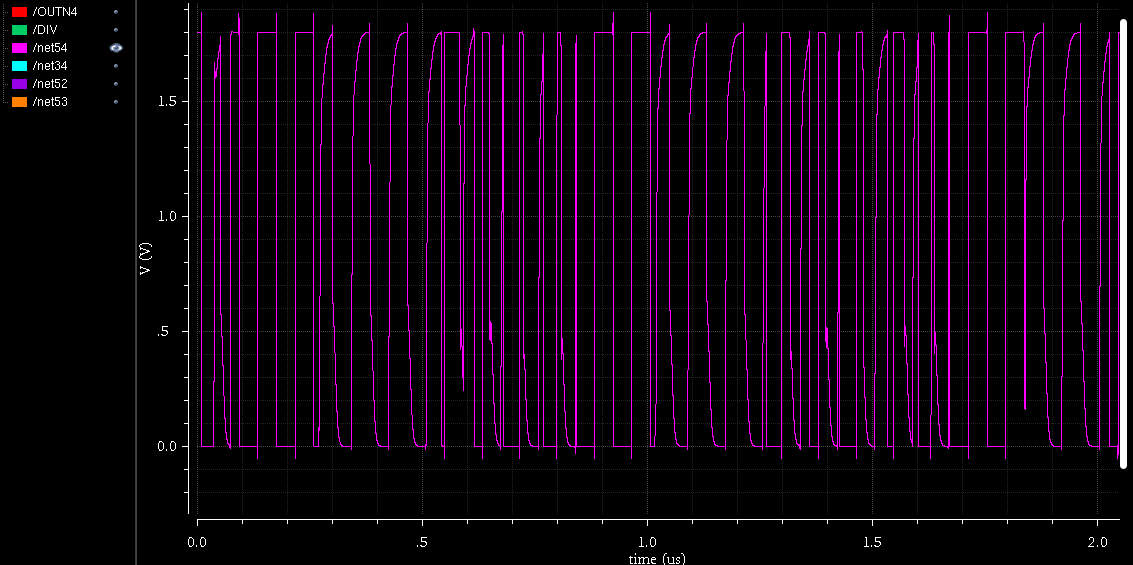

首先是参考频率的波形

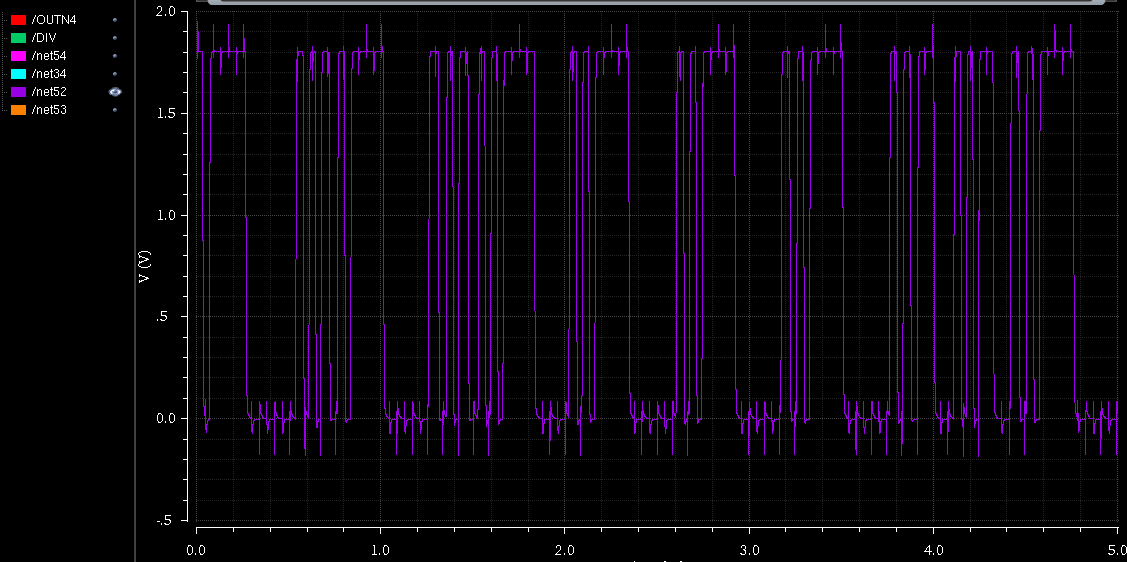

然后是分频器的输出波形

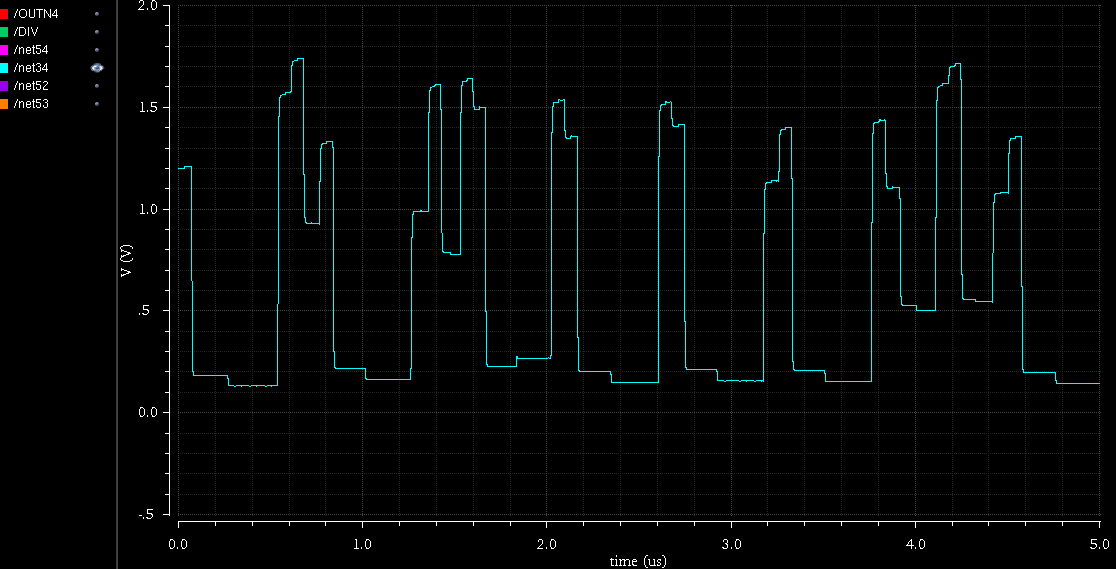

两者经过XOR之后变为

最后对应的vc波形为

呈现了无法锁定的状态,我用的XOR就是一个异或门

参考频率的好像没发上,就是理想的vpulse信号

假设你的xor有足够的驱动能力来驱动后面的lpf,从波形上来看,ref参考频率10Mhz,simulink上标的rc时间常数是5.21n,如果电路上也是这个值的话,那么这个lpf的-3db带宽是31Mhz?

参考频率是12MHz,对于lpf,主要还是后面的零阶保持器,采样频率为12MHz,对应的3dB带宽是5.2MHz,前面的5.2ns那块对环路的影响比较小,基本可以忽略。结构就是一个XOR,一个零阶保持器,然后就是vco+divider,整数分频。

对于XOR我用的尺寸已经比较大了,60u/400n左右的级别,但是还是感觉经过XOR后信号的上升与下降都需要较长的建立时间,还是驱动能力不太够?这个会影响到整个PLL的锁定么

simulink仿真环路的相位裕度为28度,虽然稍微小了些,但是应该不会是因为这个问题导致无法锁定吧?

这个环路的open loop bw和dominant pole是多少呢

开环的单位增益带宽是3.9MHz

书上都会讲gbw要小于参考频率的1/10

可以考虑xor输出加buffer缓冲

另外很好奇你的simulink上xor后面有个增益级1.8,这个怎么来的

不知道你的一阶rc滤波怎么取值的,lpf的截止频率不是远远小于12Mhz的话怎么能把Vc上的纹波滤掉呢

谢谢分享

这个是一类PLL,用的LPF结构是MSSF结构,并不是简单地一阶rc滤波,它可以实现大的带宽,而且不用担心VC的纹波;

1.8是我加的,因为实际电路XOR的输出就是1.8V的信号,也可以把两个输入信号直接变成1.8V的就行;

我试一下加一个buffer看看,波形应该会改善,还要看看能不能锁定

加了buffer以后还是不能锁定