关于锁相环环路延时对于锁相环影响的问题

时间:10-02

整理:3721RD

点击:

最近在研究锁相环,在对锁相环的simulink模型仿真时,想看一下在环路的各个位置加入延时对于锁相环性能的影响。当我在VCO前加延时后,锁相环锁定速度变慢了,这也很好理解,无非是由于VCO的“惯性”导致参考时钟和反馈时钟的相位差符号改变(由负变正或由正变负)时VCO频率变化没有及时改变方向。但如果想学术性的探讨这个问题,那这个延时是对什么性能造成的影响呢?是带宽?增益?还是什么?使得锁相环锁定时间变长了。请前辈们赐教

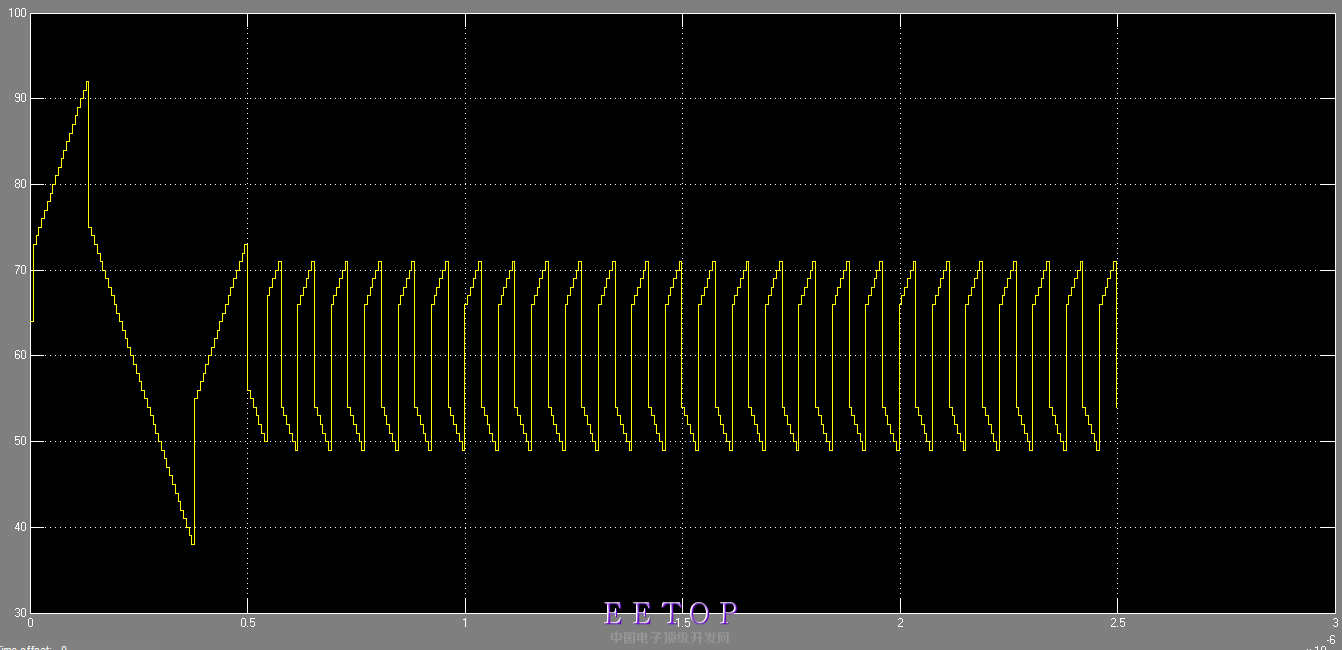

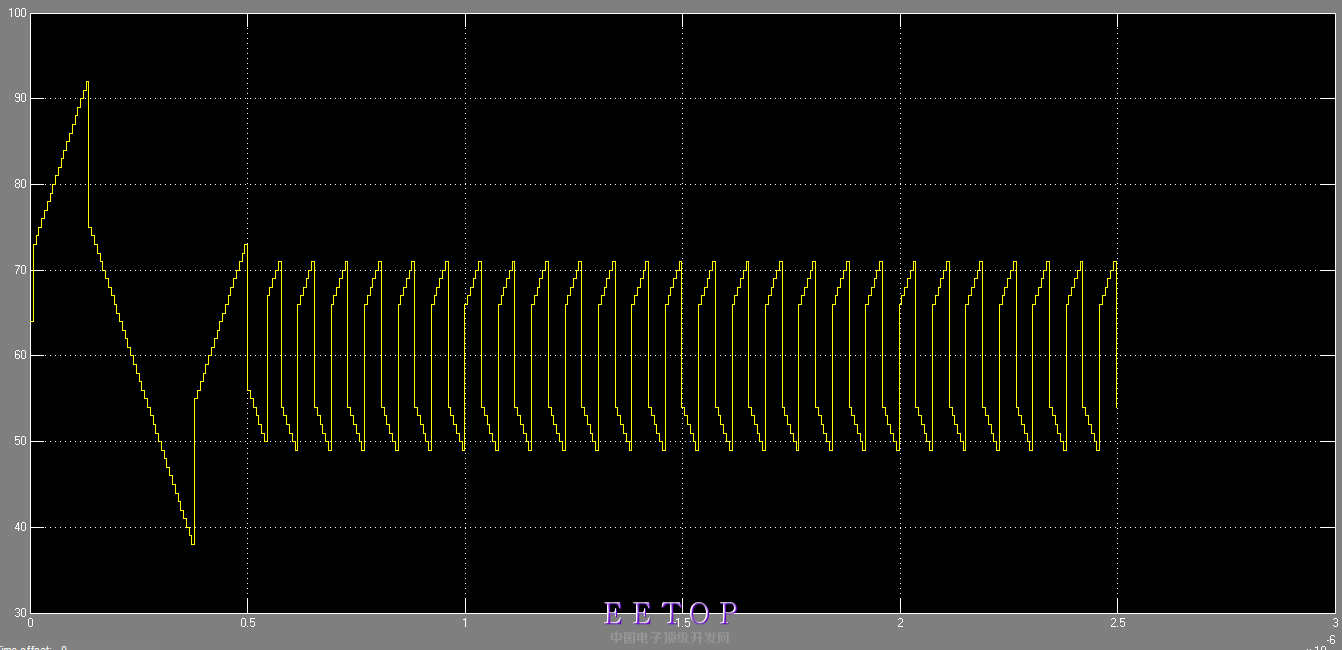

增加5个参考时钟的延时

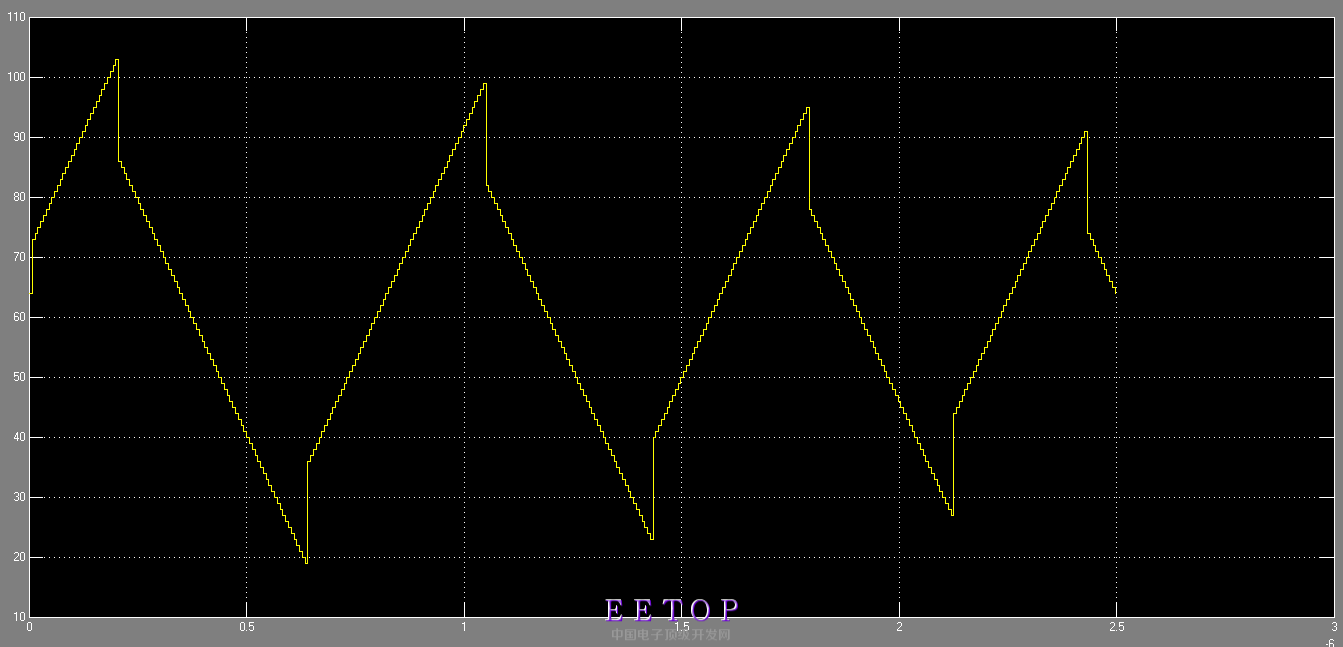

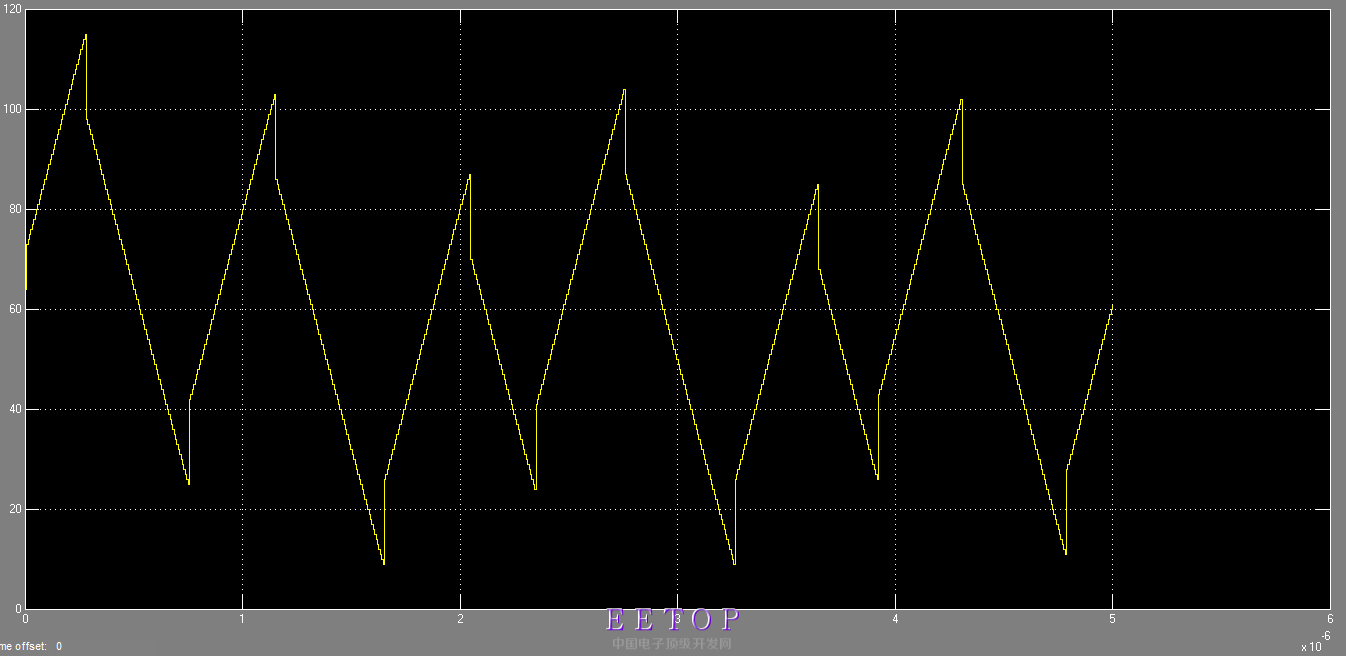

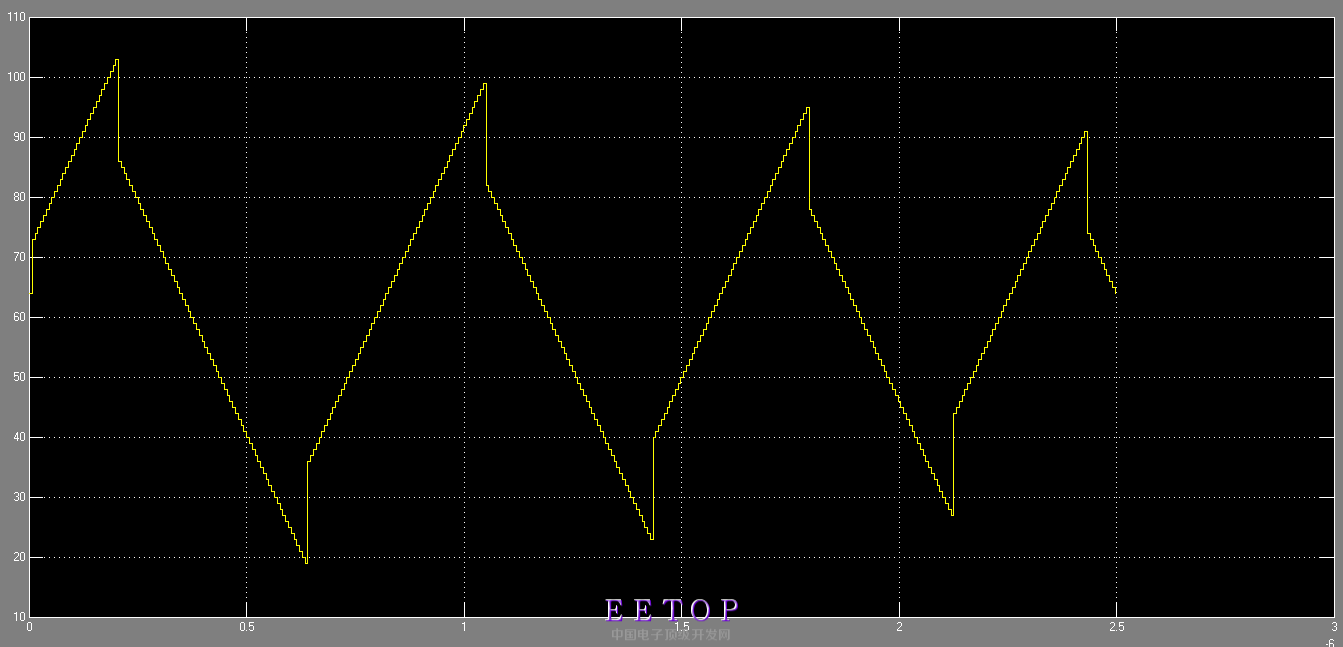

增加10个参考时钟的延时

后两个情况因为memory限制仿真时间不能再增加了,所以没追上。

在现有结果上,我注意到两个地方,第一是最后一张图(10个参考延时)很奇怪,不是简单的初始相位差增加的影响,可能是PFD每变化一次方向,导致一个相位差变化

第二个是前两个图对比,如果仅仅是初始相位差的区别那么在他们锁定后,理应没有区别,但是两个图在锁定后,“小台阶”的个数增加1参考延时的比0参考延时的多了一个,所以我感觉有可能是PFD每变化一次方向,导致一个固定的相位差增加。这样解释是否合理一些呢?非常感谢您给我的帮助和启发。

PS:这个锁相环仿真是ADPLL,用的BB-PFD+数字滤波器(累加器)+VCO+整数分频器,为了消除量化噪声对此次仿真结果的影响,同时让锁相环尽快锁定,我将积分路径的增益设为1,比例路径的增益设为8,VCO增益为5MHz/V.

stability

个人理解,延时的加入仅仅改变了pfd的初始相位差。锁定时间变长也是由于初始相位差增大的缘故,并没有改变环路带宽增益什么的。当然了,以上讨论仅针对delay时间是恒定的与频率无关的,如果delay时间与频率相关那另当别论。

能说的详细些么?毕竟稳定性包含了太多内容

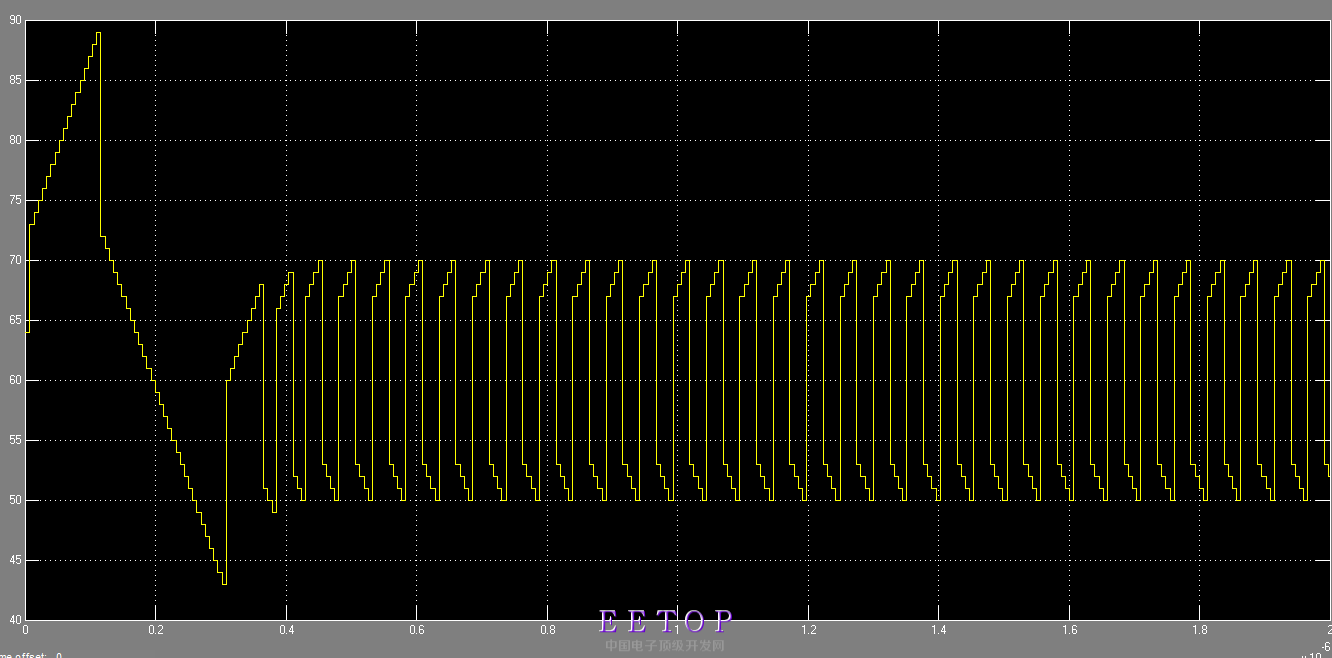

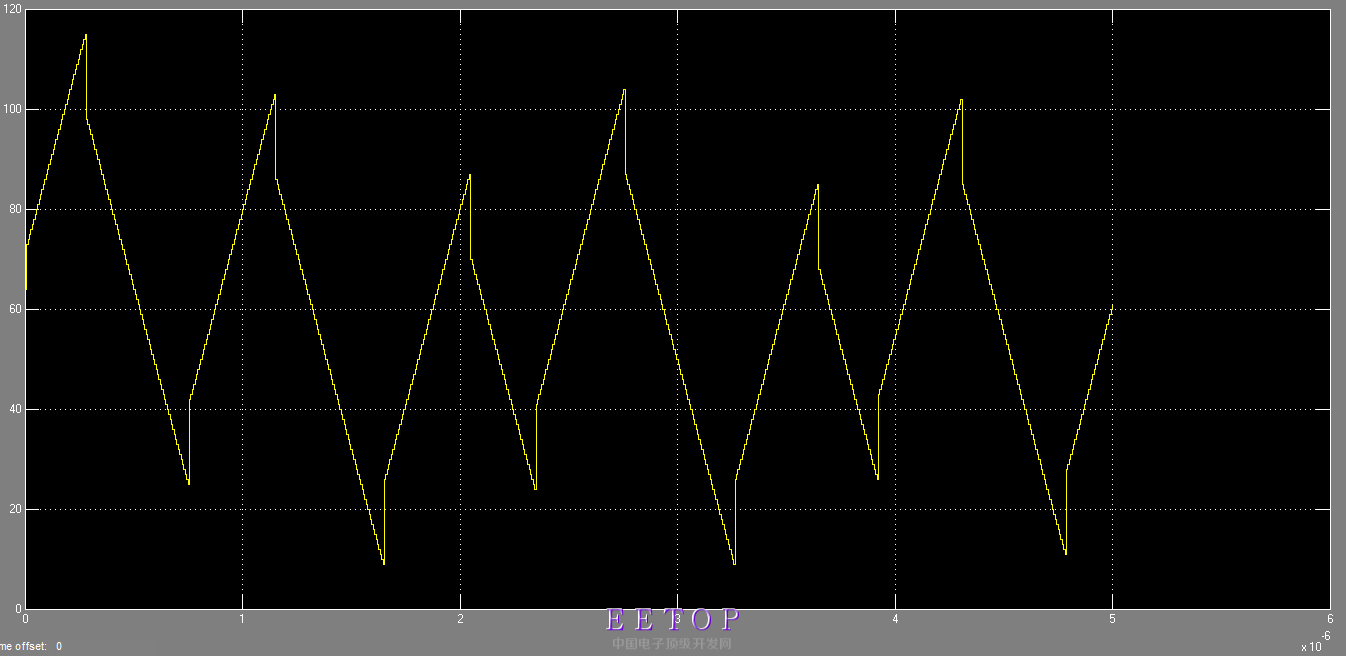

感觉如果单纯是相位差的增加不太对,我仿真了一下,得到下面一组图,分别是不另加延时

增加5个参考时钟的延时

增加10个参考时钟的延时

后两个情况因为memory限制仿真时间不能再增加了,所以没追上。

在现有结果上,我注意到两个地方,第一是最后一张图(10个参考延时)很奇怪,不是简单的初始相位差增加的影响,可能是PFD每变化一次方向,导致一个相位差变化

第二个是前两个图对比,如果仅仅是初始相位差的区别那么在他们锁定后,理应没有区别,但是两个图在锁定后,“小台阶”的个数增加1参考延时的比0参考延时的多了一个,所以我感觉有可能是PFD每变化一次方向,导致一个固定的相位差增加。这样解释是否合理一些呢?非常感谢您给我的帮助和启发。

PS:这个锁相环仿真是ADPLL,用的BB-PFD+数字滤波器(累加器)+VCO+整数分频器,为了消除量化噪声对此次仿真结果的影响,同时让锁相环尽快锁定,我将积分路径的增益设为1,比例路径的增益设为8,VCO增益为5MHz/V.

小编好人一生平安

ADPLL没有涉猎过,之前讨论的基于CPPLL,抱歉

感觉原理上应该是共通的吧。我再想想。谢前辈!

offset

多多交流~

不太明白,offset指的是?

会改变你的stabilitty的,你在写discrete model的时候腰加上的,如果换算下的话,一个dff增加一个z^(-Tref/Tsample)好像,公式有点忘了,等效是degrade你的PM,比较典型的是在divider上。不过一般你不考虑,5,6个DFF的延时不会有什么实质的改变应该

多谢指点~

小编好人一生平安