晶体振荡器设计

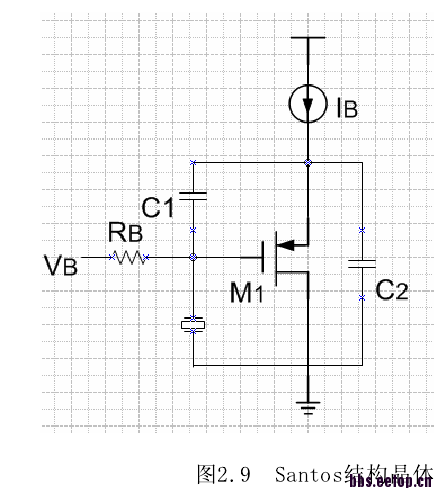

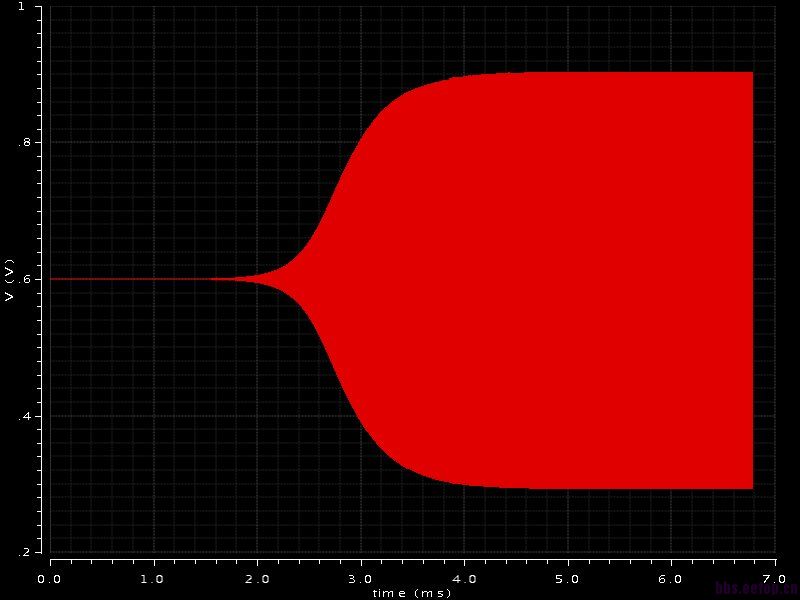

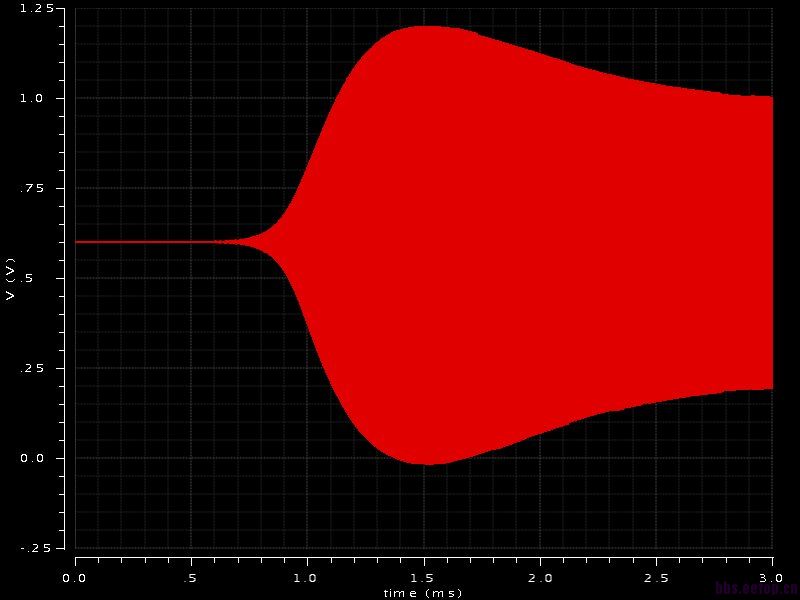

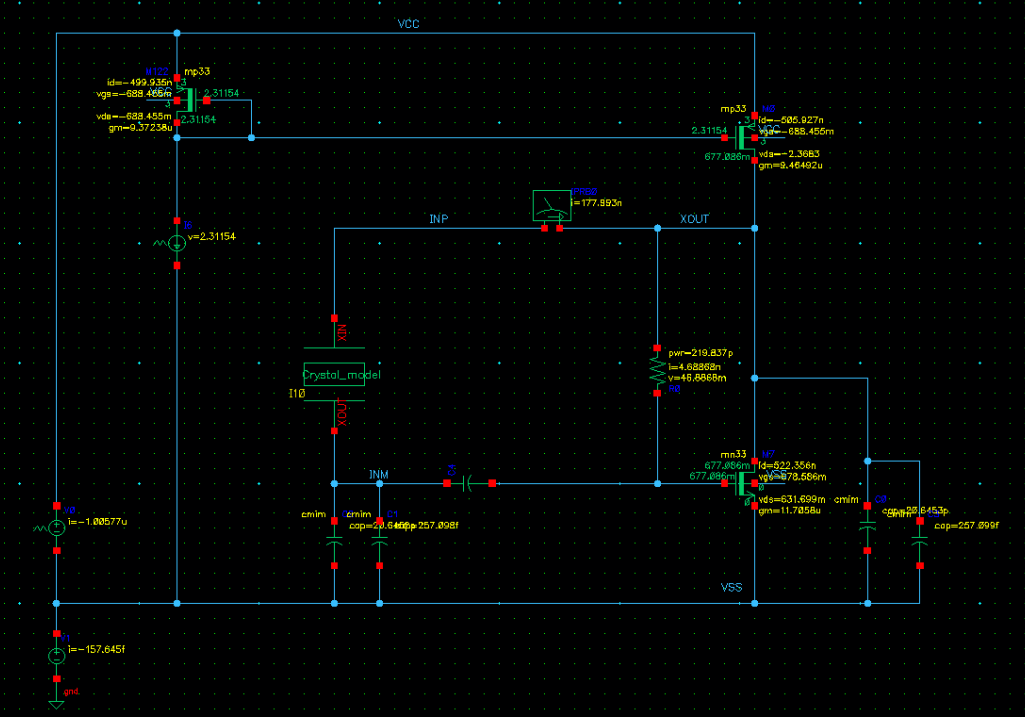

加了AGC之后也就是如图电路图中的regulator之后,仿真输出波形如图

两种情况都可以产生稳定的输出方波,并且两种情况输出频率精度也一致,相位噪声也一样,那请问在晶体振荡器的设计中为什么还要多加一个AGC这样的自动限幅电路呢?是不是为了稳定输出频率即稳定输出频率牵引因子,抗PVT?求大神解答,不胜感激!

你的第一张图上仿真用的是理想电流源吗

功耗啊

不是,用的PMOS管,然后在栅极给一个偏置电压

谢谢你的回复,我起振阶段上面偏置电流比较大,目的是为了顺利起振,稳定之后通过调节偏置电压使电流减小,所以稳定之后的电流小相对来讲就可以减小功耗,功耗消耗比较大的地方其实是起振阶段,因为电流大。稳定之后功耗就小了。所以整体看来可以大大降低功耗。请问你的意思是这样的吗?

对的。

谢谢你,我还有一个疑问一直搞不懂,为什么晶振起振要这么长,甚至长到几ms,电源上电,放大管的跨导迅速升至起振所需要的跨导值,应该会立即起振啊,为什么前面这么长一段的时间都是直线呢?求大神指教

前面是靠电路噪声的,电路噪声水平大点启动会快点。由于Q值很高启动总是很慢的。

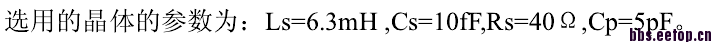

LZ晶振的模型参数是什么样的。我网上down的很多参数模型都无法起振,必须认为的修改才行。

赞一个。

[img]file:///C:\Documents and Settings\Administrator\Application Data\Tencent\Users\531672604\QQ\WinTemp\RichOle\]CM4A[}NV27D79~HK_@_U4D.png[/img]

[img]file:///C:\Documents and Settings\Administrator\Application Data\Tencent\Users\531672604\QQ\WinTemp\RichOle\]CM4A[}NV27D79~HK_@_U4D.png[/img]

请问AGC如何实现的?谢谢

你好,再请教一个问题哦,如果提供偏置的Rf是接在mos管的源漏两端,用stb来看环路的相位差,可以直接在gate打断吗,这样看的话,是不是只要0db时相位在45度以下就可以了

不清楚你说的什么

嗯,嘿嘿,描述得不好,

这里想用stb看电路能不能振荡,

在INP这条线上加iprobe和在XOUT这条线上加iprobe的区别是什么呀,

是只要0dB的时候,相位小于45就可以振荡么

区别是有没有把反向器的反馈断开。DC是还要有增益,等等。一般计算负阻。

嘿嘿,谢谢回答呢~额,不过咱还是有点懵,“DC是还要有增益”这个是什么,嗯,是按照sansen书上那样计算的gm,能工作,还是很有点混呀,晶振两端接地的这两个电容是什么作用呀,嘿嘿