LDO环路中这种补偿电容接法的目的?

时间:10-02

整理:3721RD

点击:

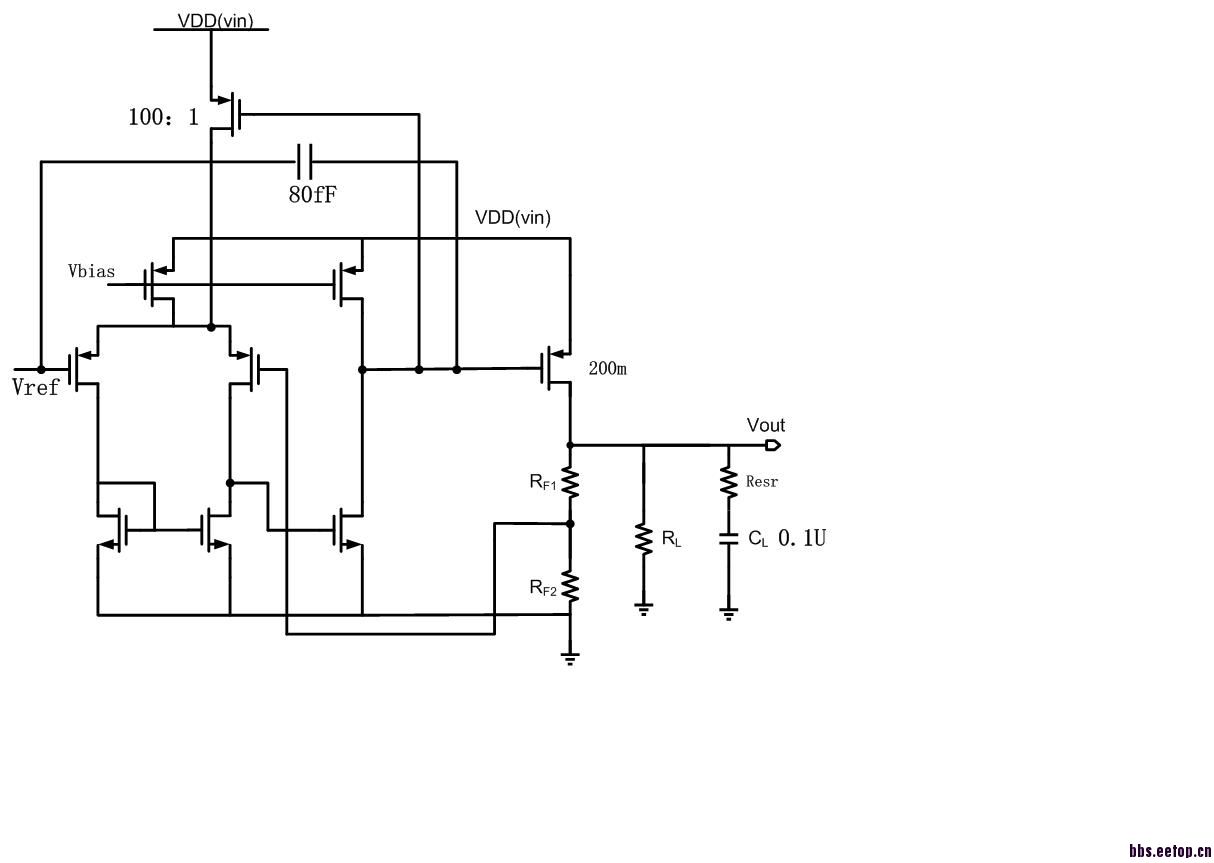

在这个电路中的补偿电容接在功率管栅端和VREF端,很少看到这种接法,有没有人了解这样、做的目的?

Hi fibonacci24:

If you remove the cap, the stability is ok or not?

mpig

zan zan

Hifibonacci24:

补偿电容接到了二级运放的负端(Vref 端)。这个电容和Vref 的输出阻抗组成了负反馈降低了这个二级运放的增益,也就降低了整个LDO的环路增益,有利于稳定性。

我不太明白你说的 这种补偿是和动态偏置结合的请问哪里来的动态偏置?

你好,动态偏置没加上去,主要是跟随负载动态调节放大器尾电流

mark mark

那个电容大小是多少啊?看不清。补偿稳定性的结构很多,这样补偿确实少见。我怎么感觉不像是用来补偿稳定性的,而像是来改善line regulation的响应速度的。你觉得呢

电容跨接在功率管栅极和参考电压之间,交流就相当于栅极对地接了个电容,对ldo似乎没什么补偿作用。如果看做跨接在误差放大器的输入输出,倒像是对误差放大器的补偿。这电路从哪来的,确信是正确的吗?还是因为小编没把必要的电路贴完整,大家也只能按断章取义的电路胡乱分析了

應該是具有Miller effect 的補償電容,在O的端點此等校電容約C1*OP gain

讓C0所產生的Pole < 10*C1所產生的Pole

谢谢, 这个电路是正确的,大致结构是这样,的确优化了相位裕度

你的主极点是在功率管的Gate端吧?那么增加电容确实只会使你的GBW更小&稳定性更高。

谢谢分享!

biaoji