运放相位裕度仿真问题

时间:10-02

整理:3721RD

点击:

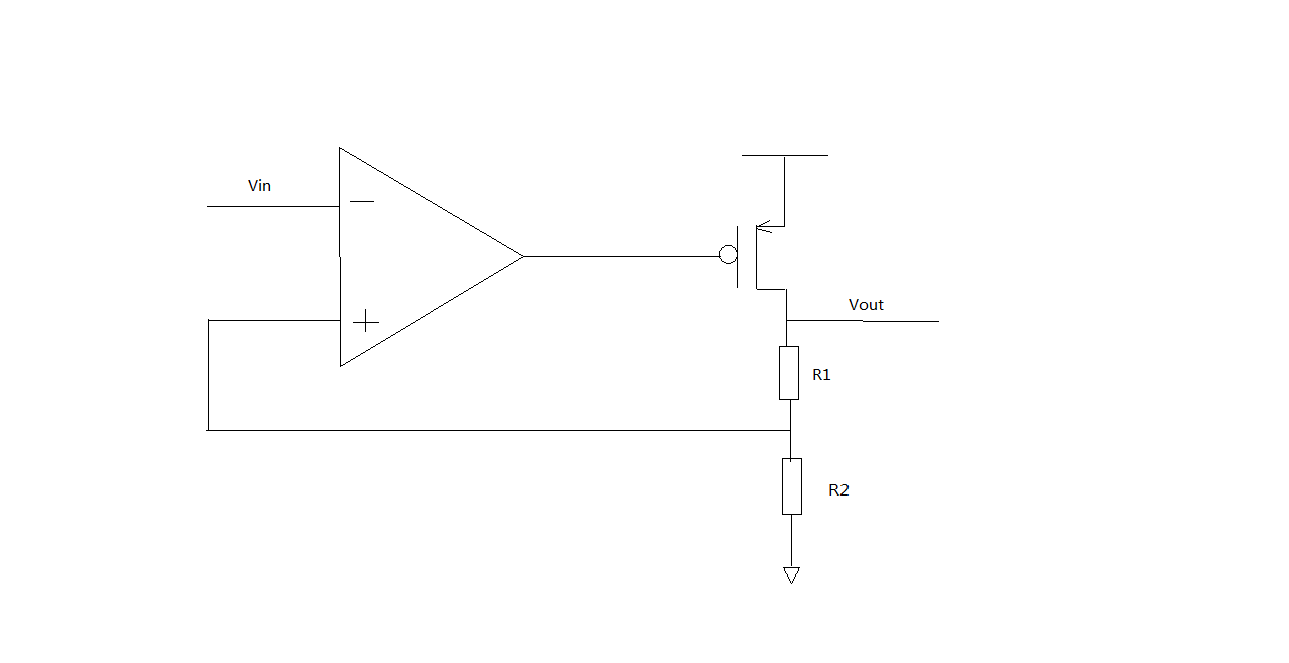

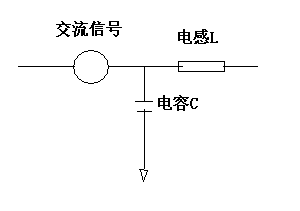

我的仿真方法是在运放正输入端添加大电感、大电容和交流信号,在没有米勒电容的情况下,仿真得到的相位裕度是19度左右,但是在时域仿真中,从Vout处来的脉冲会造成运放自激振荡,不会衰减。添加米勒电容,将相位裕度调整至60度左右时,时域仿真上还有几个周期的衰减振荡波形。

请问这种相位裕度仿真与时域仿真不匹配的情况是怎么回事,该怎么解决。

没仿对吧,我仿这种环路还是选择断开,在一端加激励,然后看环路的增益和相位情况

断开仿真也试过,结果一样。

断开怎么仿的具体?你试试stb仿真

AC仿真是的DC工作点 是否和trans仿真的最终状态一致?

按照书上的仿真方法,将上图两端串接在断开处,这样既可以保证直流工作点,同时在高频时,电感相当于断路,电容相当于短路,就相当于断开加测试信号。

试一下用analoglog lib里的iprobe器件,串在电阻反馈和运放输入正端,仿stb

试试用analogLib库里的iprobe器件,串在反馈电阻和运放正输入端,仿stb

1.检查仿真是否正确

2.PM是60度不代表时域响应就好

2L那个图难道不是仿的闭环响应吗。

仿真方法不对,你这接法激励都泄到地上去了。

hspice:运放反馈端断环做ac仿真

spectre:运放反馈端加iprob。

在R1和R2之间的节点和Vin+之间断环,或者试试9#提出的STB仿真