差分运放共模输入电平由什么决定?

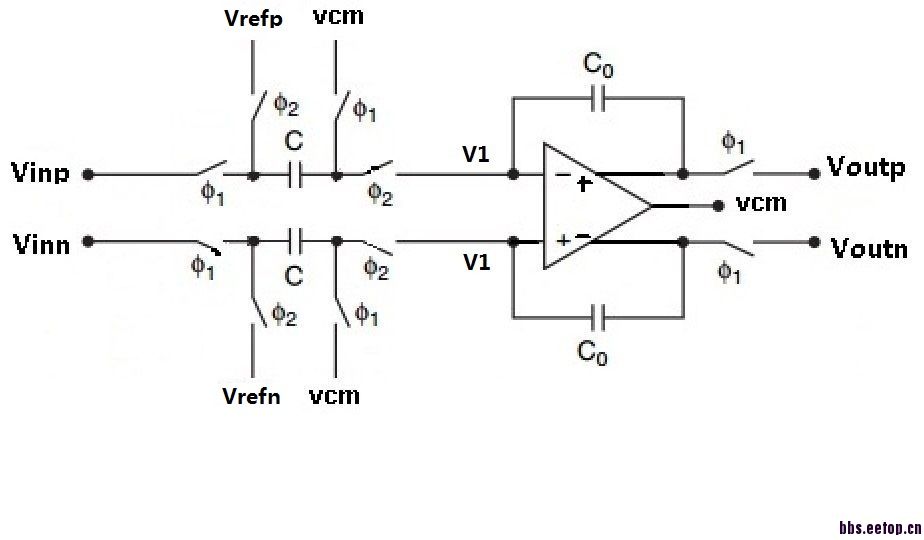

全差分switch-cap结构的sdm第一级integrator的输入共模电平Vcmi是由什么来决定的?电路结构如下图,用全差分结构实现,Vcmi应该就是图中的V1,由于运放高增益和反馈,两个输入端是相等的电压没有问题,,是虚短概念,问题是V1值是多少,也就是Vcmi的值是由什么决定的?

我想运放内部应该没有决定Vcmi的机制,CMFB可以决定输出共模电压Vcmo(本图中Vcmo=Vcm),是不是Vcmo通过外部的SC反馈网络,由某种机制决定的Vcmi?

可是没想明白的是,电容是隔直的,运放两输入端又都是高阻节点,这个直流的Vcmi是由哪里给出的呢?

这个问题不仅局限于积分器,对于通常的采保结构也同样存在,大家都来分析一下吧。

我认为共模电压Vcm不是电路“给”的,而是按照电路的输入信号叠加出来的,按照共模电压的定义应该是(Vin- + Vin+)/2。

上面的这个开关电容结构,Vin+固定为0,Vin-接Vin是上一级信号,两者相加平均就是共模电压大小。

另外,图中的运放是单端输出,对于这中运放是没有CMFB这个概念的,小编你要知道CFMB是用来稳定输出“共模”电压的,这是一个单端的输出,何来“共模”的概念?

肯定是电路给的咯,电容又没有直流反馈。把全差分的电路画出来,传上来,就应该知道了

我在“给”上加了引号,我的意思就是说,一个差分运放的两个输入端是确切的实际输入值,共模、差模输入的概念是对着两个信号人为的区分出来的。上面的这个电路,Vin 直流信号完全过不来的话,输入共模就是0,如果要单仿这个运放,就把仿真时的Vincm设置为0V,这是我的理解。

不是的,这是开关电容电路,采样phase下,运放另一端会接“地” 这个地就是opamp的共模输入

还不就是0

楼上的几位兄弟,我把图更新为全差分结构了,要讨论的也是全差分结构,单端输入很好理解的,运放一个输入端接地,应用运放虚短概念,就可以完全确定另一端也是地。但是全差分结构中,运放的两个输入端V1、V2都处于高阻,虽然也是V1=V2,但具体值不知道,我初步认为是通过外围反馈决定的,应该有V1=V2=Vcm,但没弄清是如何推导出来的。

欢迎大家踊跃发言,都来分析下。

好问题

你 Phase 1 的时候,不是已经画出来了么。是VCM。就是Vcm呀 。输入共模和输出共模可以不同的。

phase 1的时候,ph2开关是断开的,V1点并不与vcm连接,是高阻态吧?

好討論 學習學習

首先,采样Phase1放大器是用不到的。Phase2时候,opamp两端输入共模电平还是VCM,感觉你连接后边 VOUT的 是Phase2吧? 为什么是Phase1?或者前边画错了。

呵呵之前的问题都还没搞清楚就换了张图?这问题问的也是醉了

电容不是隔直的,是用来消除input offset用的

学习了

ota后面的开关是phase1,否则积分阶段就会和下一级采样连接,是不对的,其实这个开关可以不看的,不影响前面的特性,当作悬空就行。你说phase2阶段,运放的共模输入电平就是vcm,为什么?能给出推导吗

朋友你好,我的主帖里一直问的都是差分结构,单端结构是很简单的,不用讨论的。一起来分析一下差分的情况吧

小编没有画出RST把。第一个周期前RST会把OP输入端清空,然后PH2D导通的一瞬间VCM传过来,然后再charge share到稳定点位。

以后每个hold phase都在原来基础上加减。所以VCM应该不同周期不一样。

v1应该和输出共模和输入共模都有关系,此外还与v1点的初始值v1(0)有关,不知道这样的观点对否?从仿真来看,无论加或不加reset开关,v1都可以建立到一个定值。

直流过不来,不代表共模是0 。共模是交流信号中相位相同的信号,而不是直流信号。你所说的应该是差分运放的输入管偏置电压。这个电压是又外部给的。此外我觉得你这个图有问题。

。

好问题