关于锁相环的环路稳定性

时间:10-02

整理:3721RD

点击:

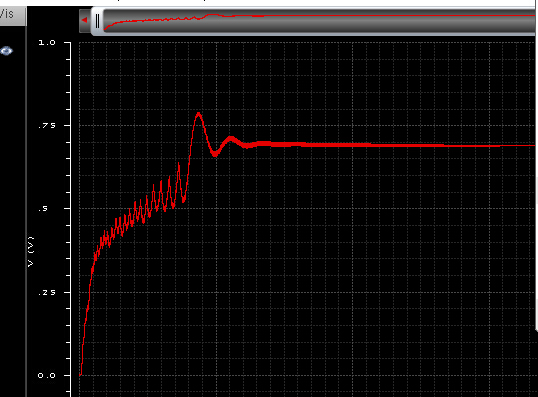

我是按照阻尼系数等于0.707而仿真出来的一个锁相环,VCO控制电压的波形如上图所示,我怎么感觉好像有一点开始衰减震荡的样子,好像环路有点不稳定了,请问这种情况算正常吗?

正常, 开始是frequency lock,后来是phase lock

你这样是正常 但是 setting time 比较长 你环路里面用的是什么 block PFD+CP?把 nature bandwidth 做大 然后那个zata 0.707做大点大概1以上 效果会好

那个nature frequency 增大 如果你是 charger pump的话 把那个 loop filter里面的 R 增大 C 减小 然后charger current不变那个VCO 的gain不变。

?

我看了一下建立时间大概20us左右,这个值应该还可以吧(我不是很清楚环路稳定速度的指标),我用的是PFD+CPblock,你说的那个nature bandwidth指的是环路带宽吗?还是指的是自然频率(本征频率)ωn?

指的是自然频率(本征频率)ωn

那个zata 就是 damping ratio (好像叫阻尼)

请问,nature frequency和loop bandwidth有什么关系?望不吝赐教!谢谢!