Verilog-A模块中端口电流定义的“奇葩思维”

时间:10-02

整理:3721RD

点击:

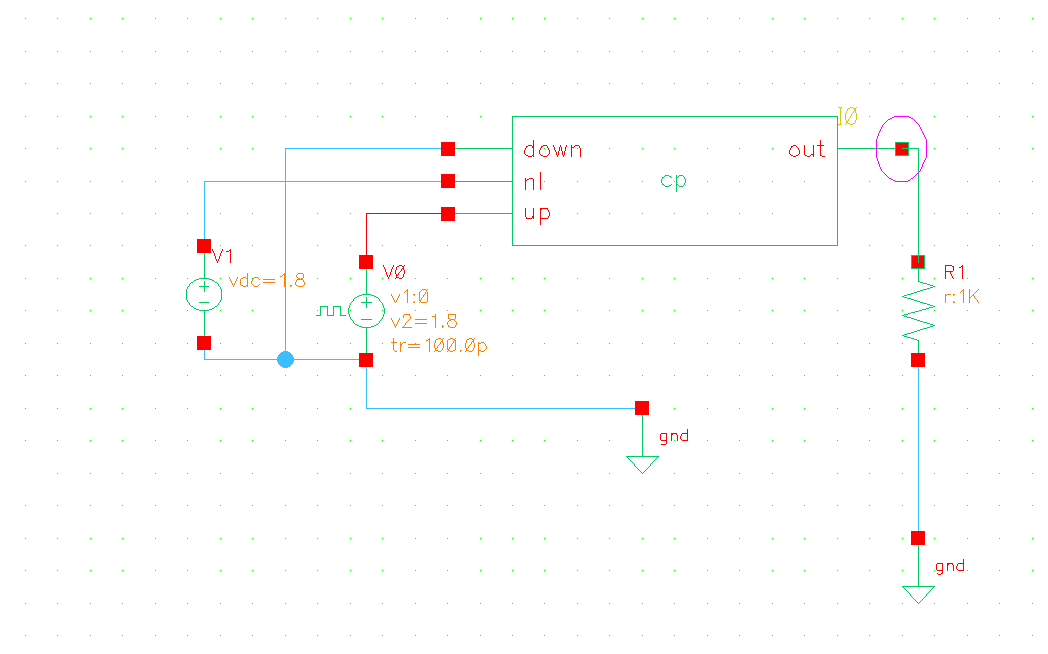

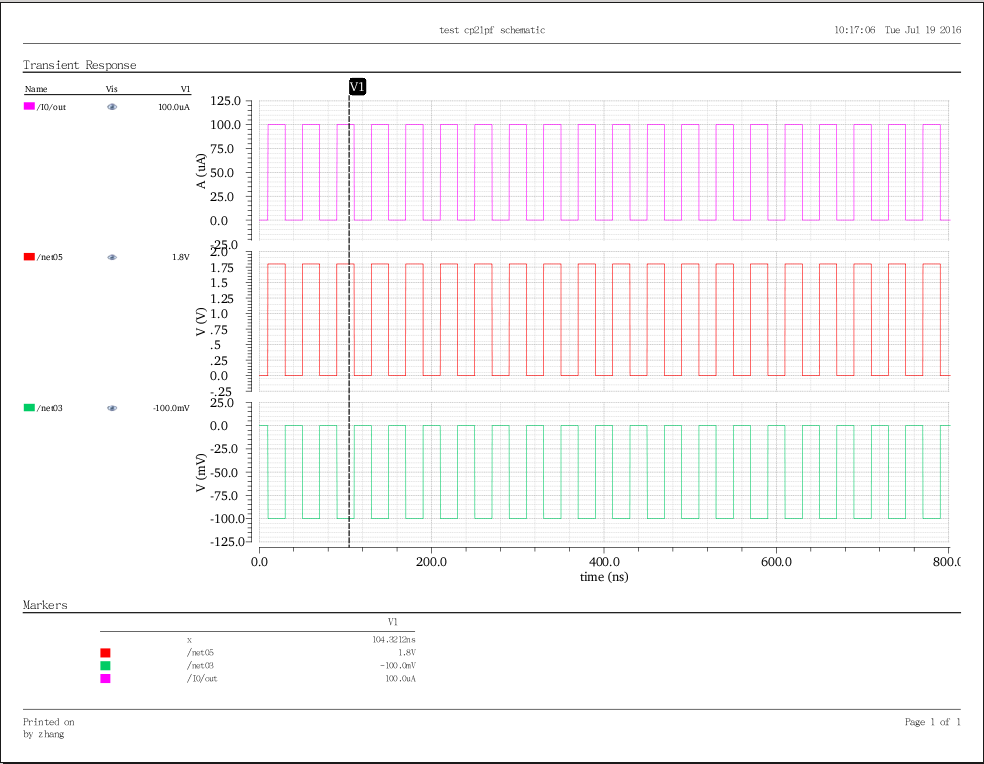

在昨天仿真锁相环时出现了一个奇葩问题。定义电荷泵的输出电流为100uA,而后面滤波器的电压却是在下降。

也就是说电荷泵这个模块是在抽取电流,而不是输出电流。这个非常的奇葩,我在仿真的时候探测电荷泵输出电流端口的电流大小,显示的是100uA。于是我另外搭建一个测试电路,用这个电荷泵的输出端加电阻负载(电阻另一端接地),最后发现电阻对地的电压是负的。而测试电荷泵输出端口的电流还是显示100uA,也就证明了,这里端口电流大小如果为正,那么代表的是外部输入电荷泵的电流(注意,电流方向是外部向模块内部),尽管在模块内部定义这个端口为输出端口。但事实上,电流的方向不是你定义为输出就是对外部输出的方向,而是相反的。

“奇葩思维”的原因是,我们使用Verilog-A描述语言,是描述电路,系统也是将它理解为一个电路模块,而真正的电路模块的端口是一个导线,导线是没有方向的。因此我们默认对一个电路的端口灌入电流的方向为正。

也就是说电荷泵这个模块是在抽取电流,而不是输出电流。这个非常的奇葩,我在仿真的时候探测电荷泵输出电流端口的电流大小,显示的是100uA。于是我另外搭建一个测试电路,用这个电荷泵的输出端加电阻负载(电阻另一端接地),最后发现电阻对地的电压是负的。而测试电荷泵输出端口的电流还是显示100uA,也就证明了,这里端口电流大小如果为正,那么代表的是外部输入电荷泵的电流(注意,电流方向是外部向模块内部),尽管在模块内部定义这个端口为输出端口。但事实上,电流的方向不是你定义为输出就是对外部输出的方向,而是相反的。

“奇葩思维”的原因是,我们使用Verilog-A描述语言,是描述电路,系统也是将它理解为一个电路模块,而真正的电路模块的端口是一个导线,导线是没有方向的。因此我们默认对一个电路的端口灌入电流的方向为正。

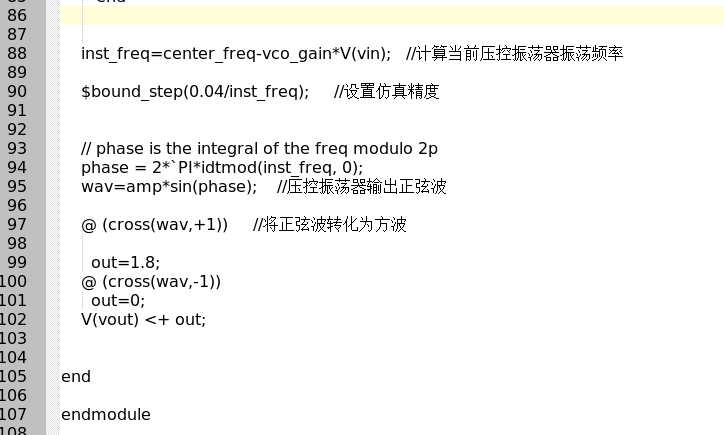

[img][/img]

确实是这样的。

当时怎么都不敢相信,后来想想也有它的道理

verilogA中对单一节点的contribution相当于把电流源或电压源加在了该节点和参考地之间.

I(out)<+ icp;

相当于

I(out,0)<+ icp;

即在out和地之间增加一个电流源, 如果icp为正值, 则电流就从out流到地.原来如此