运放电路发现一个大问题

大家好!是这样的,今天在仿真中遇到了一个很烦恼的问题,工艺是smic 0.13 在温度=22度,我的运放输入电压为0--3.3V(DC扫描),运放接成电压跟随器的方式,前端仿真输入电压=650mv时,输出的误差在7.465mv ,输入电压=1.65v时,输出的误差在175.7uv .但是在后端版图仿真的时候 输入电压=650mv时,输出的误差在27.41mv ,输入电压=1.65v时,输出的误差在22.12mv.前端和后端仿真失配特别大,请问大家遇到过这种情况么?懂的话麻烦解析下,这是什么原因?谢谢。

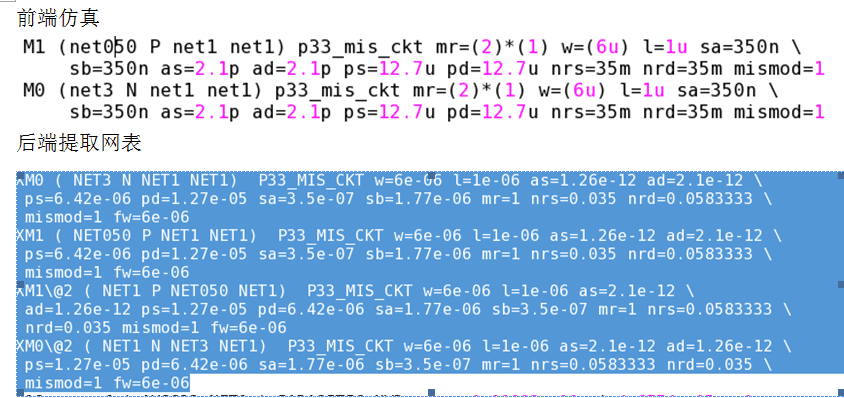

图片为前端和提前参数后端的网表,可以帮忙看看有没有问题吗?

要看你运放的结构,以及版图的绘制水平

是n管还是P管输入。前仿没问题的话,这么少的信息,只能觉得是版图哪一块的问题啊

P管输入

是不是增益变小了?寄生电阻导致的?

后端是no rc (calibre提取的)

smic 0.13工艺提取时是要设置什么吗?

运放接成电压跟随器的方式,前端仿真输入电压=650mv时,输出的误差在7.465mv

不知道你是轨到轨的还是什么结构,这误差也太大了,此时运放工作可能不正常了

不是轨至轨的。是P输入的折叠式,工作在低功耗状态下,临界亚阈值区。

第一次走0.13工艺,其实我主要是想讨论前仿跟后仿为什么差别那么大,而且我还是在没有提取RC的情况下,是我提取流程问题还是其他设置等问题?希望大家帮忙一下,谢谢。

不是轨至轨。是P输入折叠式结构运放。由于是低功耗的带隙运用,管子临界亚阈值状态.电路在1.65V时,误差是175uv

低频的后仿有指导意义?

你的sa 和 sb 在提咯之后两个管子不一样,你可以尝试加些dummy或者看是不是layout 里面走线Drain,Source是不是对称的。

你的sa 和sb 不同, 可以试着加点dummy或者看是不是对称的layout

看了这么多,我还是先建议小编认真研究运放版图,我感觉运放版图是非常难画的,需要足够的经验

sa sb是LOD参数

as ad ps pd是源漏参数

主要看需要匹配的管子 参数不匹配的话 就会产生误差

如果误差太大 整个性能就坏了

不过我很好奇为什么后端提出来的网表只有这两个参数 WPE OSE PSE PMET都没有。

或许可能和layout有关的LOD效应有关, 可以看到前后仿网表中mos管的sa,sb参数不同, 可以先试试注释掉后仿网表中所以的sa,sb参数仿真看看, 如果结果和前仿一样, 那就是与这个有关了. 然后再定位是哪些关键管子造成的.

p管差分对在输入电压比较低时应该表现很正常才对,你这里已经差了7个mv,不清楚你的应用环境,我认为这个运放前仿已经工作不正常了。 另外如楼上几位所说,你的后仿网表提出的参数不对称,要检查layout,需要match的管子是否严格匹配。

这个提取的是NO RC的网表

我也怀疑SA/SB问题,你可以把网标里所有的sa /sb都改成2e-6,2um,再看看。

smic工艺这个影响还是比较大,模型仿真时。

以前遇到过这样的问题,做extraction时选了no r,no c,no cc,no l,正常情况下后仿和前仿应该没有太大差别,但是如果差别很大,可能是extraction的参数设置问题,也可能是extraction软件的问题,我当时用的calibre

谢谢!按照你的思路,把后端提取的SA跟SB参数改成和电路一致,这样的话后仿跟前仿差不多(NO RC情况下)。那么问题就来了,我版图里面的管子是有合并的,在后端提取参数的时候,导致SA和SB跟电路会不同,是不是在提取参数的时候需要设置呢?或者说XRC规则文件哪里需要修改?望指教。

原理上来讲,没有带重负载情况下,dc gain 应该不高;或是dc gain可以,对负载而言,运放输出能力不够。

此外,跟随器形式使用方式,信号电平直接影响电路工作点,不同工作点会导致增益会有差异。

确实如你所说,我后端提取的网表,把SA和SB都改成和前端一样(手动修改网表的),这样就没有问题了。但版图的实际情况,管子之间是有共用的,导致SA和SB都跟电路不匹配,请问要怎么样让后端的LOD跟前端保持一致呢

可以试试对比较关键的信号通路的管子通过两边多加dummy增加信号管的SA,SB(SA,SB越大, STI stress影响越小)来改善.

在bbs里搜索"LOD" 和 "proximity effects" 可以看到更多信息.

http://bbs.eetop.cn/thread-284392-1-1.html

先進製程LOD & WPE影響類比電路設計,介紹SA,SB,SC之BSIM4參數使用說明