HBM测试讨论

时间:10-02

整理:3721RD

点击:

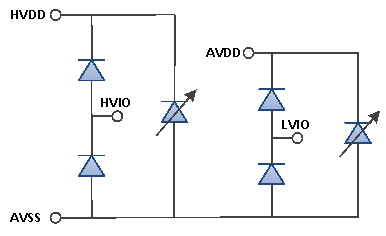

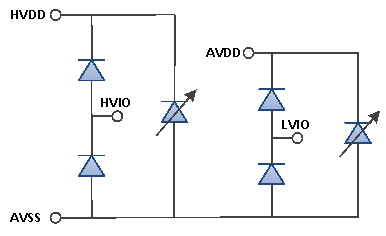

各位好!最近拿片子做ESD HBM测试,拿到测试结果后,发现了一个比较奇怪的问题,这个芯片等效ESD架构图如下:

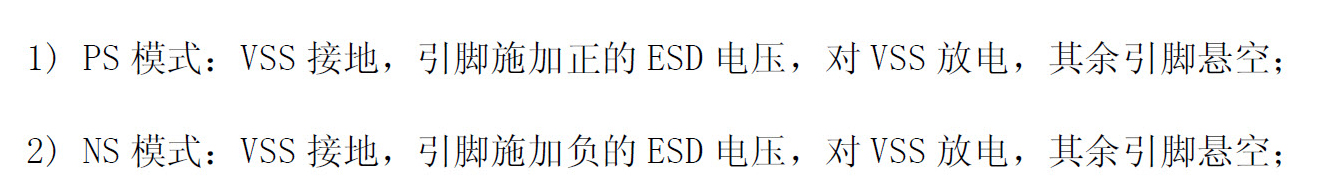

测试发现,HVDD到AVSS(+)和 AVSS到HVDD(-)的测试结果不一样,

他们的泄电回路是一样的(差别在于测试IV特性曲线时参考点不一样),

为啥HVDD到AVSS(+)可过2KV,而AVSS到HVDD(-) 1.5KV没过呢?

有其他不明白的信息后续补充,这问题可能比较小白,还请大神讨论~指教~

上图中D2和D3为高压diode,类型一样; D1为高压BJT Power Clamp.

我赞成可能悬空IO的初始电位导致了结果不同,

而为什么AVSS向HVDD打负电压,D2和D3会同时击穿呢?

测试发现,HVDD到AVSS(+)和 AVSS到HVDD(-)的测试结果不一样,

他们的泄电回路是一样的(差别在于测试IV特性曲线时参考点不一样),

为啥HVDD到AVSS(+)可过2KV,而AVSS到HVDD(-) 1.5KV没过呢?

有其他不明白的信息后续补充,这问题可能比较小白,还请大神讨论~指教~

AVSS往HVDD方向打正ESD只需要经过两个正向二极管,应该保护能力更好才是

AVSS往HVDD方向打负esd

是不是触发其它的BJT啥的咯,这玩意光看电路图是看不出来的啊。

可能悬空I/O的初始电位导致了结果不同吧

HVDD2kv0V

AVSS0V-2kV

HVI/OOV0V

因为D1是p+ nwell ,D2和D3是psub nwell,所以D1的击穿电压应该比D2 D3低,

当HVDD向AVSS打正电压,D1会先击穿,分担了一部分的电流,然后D3再击穿

AVSS向HVDD打负电压,D2和D3同时击穿

不好意思,没有详细介绍diode具体类型

上图中D2和D3为高压diode,类型一样; D1为高压BJT Power Clamp.

我赞成可能悬空IO的初始电位导致了结果不同,

而为什么AVSS向HVDD打负电压,D2和D3会同时击穿呢?

说错了,以为是标准CMOS工艺呢。那D2和D3的击穿电压相比D1怎样啊,D1这种power clamp是击穿导通吧,不像一些CMOS power clamp是直接导通的吧

ESD 性能还要看芯片布局,有时候芯片布局比电路重要。

D2和D3的击穿电压比D1高,D1是击穿导通,不是直接导通。

谢谢,从电路和测试结果分析,确实太混乱了,我再从版图方向看看。

AVSS向HVDD打负电压,同时击穿D2,D3,可能有两个原因:

1. D1的响应速度慢于D2,D3

2. D1的尺寸过小,不足以把所有esd导入AVSS,而剩余的charges相对于D2,D3来说又太大,所以D2,D3被击穿

谢谢分享