差分CML输出缓冲问题

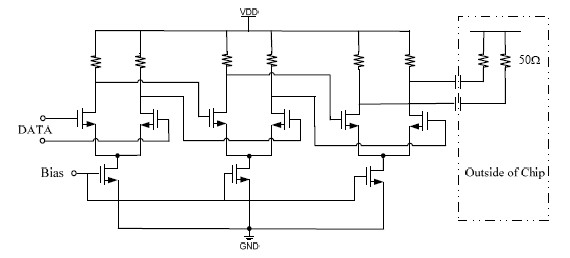

如图是数据输出缓冲电路,我用cadence仿真时,数据输入用的正弦波,发现最后输出总是摆幅非常小,试着换成两级后也是如此

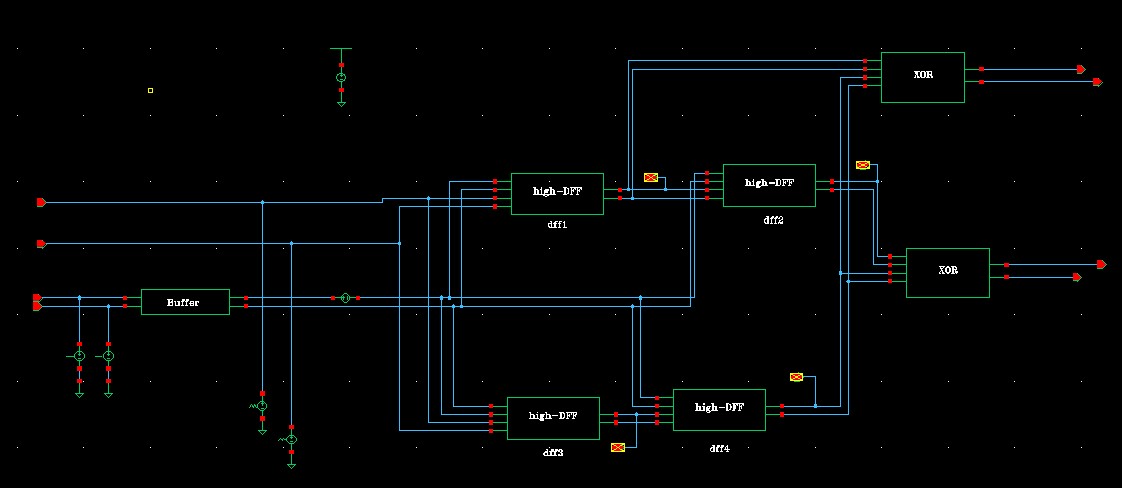

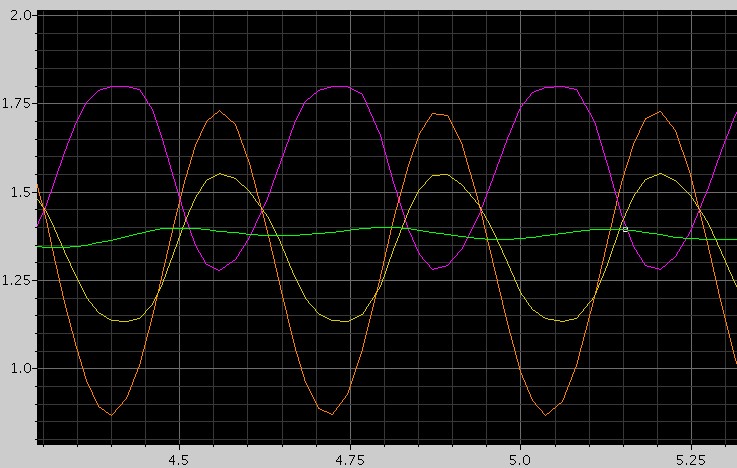

图中,粉色是数据输入,黄色是第一级输出,蓝色是第二级,白色是最后输出。

本人菜鸟,望高手指点,谢谢!

首先检查直流偏置对不对!

调了,都在饱和区

这种全差分结构不是需要CMFB的嘛

怎么会变小呢?照理不会啊?这类结构很常见

不需要,它是放大数字信号,不是有固定增益的反馈

你说“,试着换成两级后也是如此”,有点奇怪,请列出你的第一级和第二级的Ibias,器件参数还有电阻数值

奥,是你的“电容”的问题!你的电容的容抗Zcap>>Rload(50Ohm),所以衰减了

负载电阻用的5K,但为什么不管两级或三级都是最后一级才衰减啊?

为什么你第一级第二级的高都没到VDD?差分对管的gate都没有被充满电吧

你的freq是多大的?自己算一算输出耦合以后大致多大!

如果偏的还多,就是前一级偏置没有给好

需要知道你的Cap和Freq的大小还有负载RES

你的电源应该是1.8V?0.18um工艺?

黄色是第一级输出,蓝色是第二级,白色是最后输出

你看,你的结构一样,但是输出的直流偏置点不同?所以你的设计还是有点问题的。

三级输出的直流电应该很接近

学习,学习。

谢谢,可能是我没有表达完整吧,我是想通过缓冲器输出一个电平和幅值符合下级输入的信号,单独仿缓冲器模块的时候实现了,所以现在是将后面一级加入了进行了仿真,后面一级是PD模块,自己感觉是因为下一级影响输出的。

我的信号频率是3.125G,用的是0.18工艺,差分对上的负载电阻用的是5K,管子间的耦合电容没有去看。

Cap的数值要知道,输出的Res 只有50Ohm,Cap的大小影响输出幅值的。

你的图再重新描述一遍!因为有个紫红色的,相位接近蓝色,但是幅度又很大,是哪一级输出!

请重新把所有输出线一一对应描述一遍!再贴一张更清晰的图出来

谢谢!

这是buffer内部电路,也就是三级的差分结构

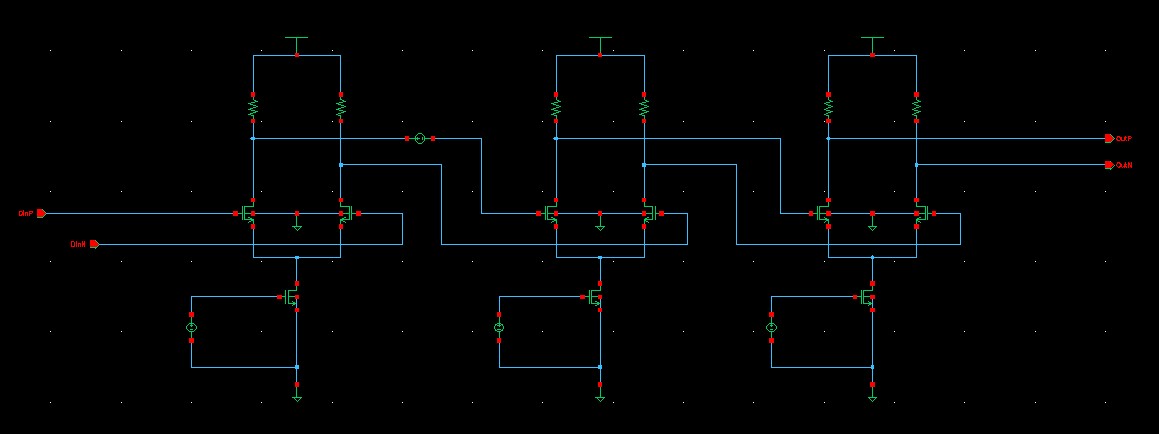

这是buffer的symbol和外部其他部分的整体电路,buffer是右下的

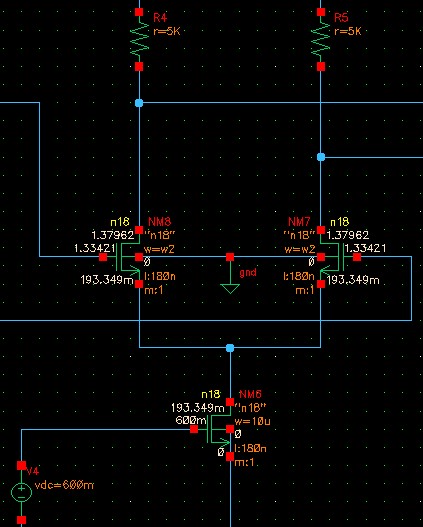

这是仿真后的局部DC参数

这是buffer内输入,第一、二、三级的输出,分别是橙、粉、黄、绿

我估计是buffer后面得模块影响其输出的

你的Ibias怎么用Vdc给的,不是用偏置电流源?你知道你的直流偏置是多少?

5k 的负载,Ibias可以是200uA左右,看你的设计需要

0.18um上3G,电流会很大

实现起来 不好做啊 up 3G

每个放大器的输入和输出直流工作点可以设置为Vdd/2.

不完全是这样!

主要是设定Vout的输出摆幅范围

timing

几个问题

1。每一级有多大增益,前级衰减可能是由于你的实际工作状态下,增益带宽不够造成的

2。耦合电容,充电状态?可能需要初始化如果想看到应该的结果

3。或者仿真时间是多久?最后级衰减多半是耦合电容状态问题,如果先跑几千个周期再看结果可能会不同。

小编不在了?

最后一级驱动50欧姆的电路,如果电流不到,输出摆幅肯定很小的

这是为什么?