全差分运放输出的一个奇葩问题

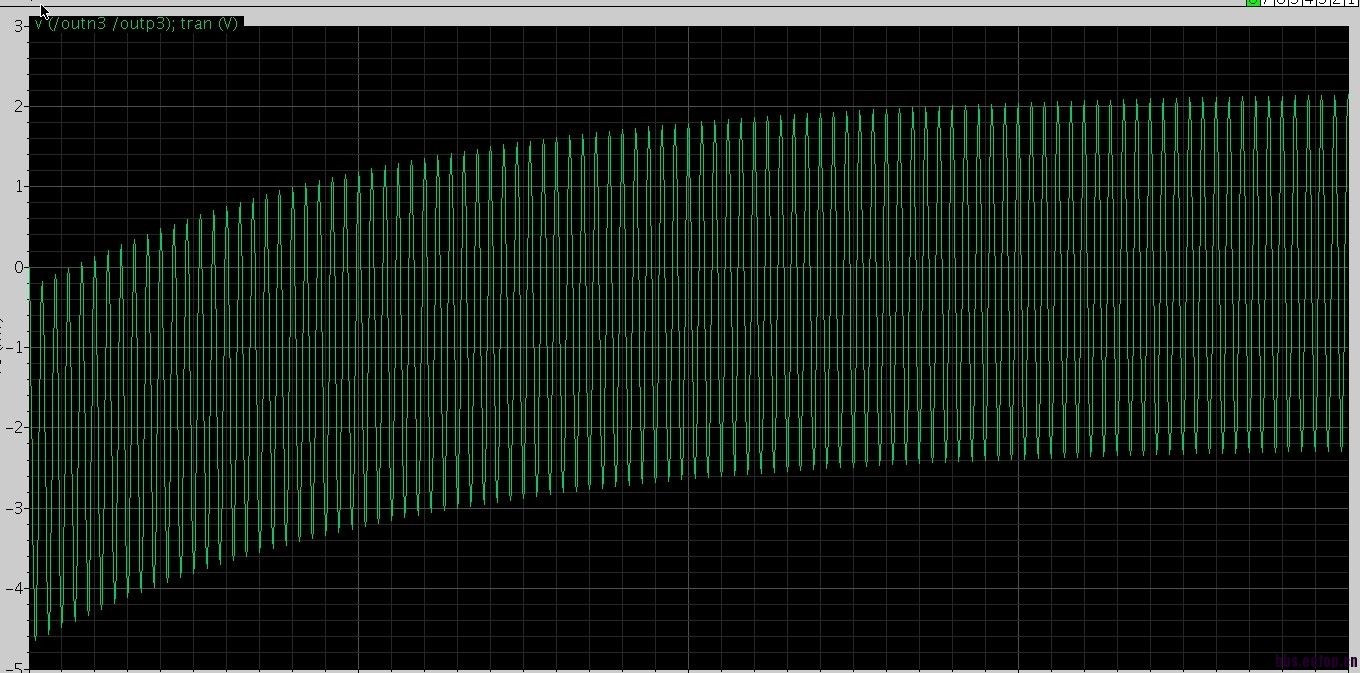

本人再设计全差分运放时,两个输出端之差(是在开环情况下,所以小弟认为应该刚开始就在零之间摆动)出现如图所示的情况,很是不解,急等高手解决。

本人再设计全差分运放时,两个输出端之差(是在开环情况下,所以小弟认为应该刚开始就在零之间摆动)出现如图所示的情况,很是不解,急等高手解决。

看起来象是电路在逐渐建立偏置点并稳定的过程,能上涨电路图,并描述一下仿真条件吗?

可以强制设一个initial condition试试

没见过开环做tran的,毫无意义

你plot一下两个单端,初始应该一个在地一个在电源

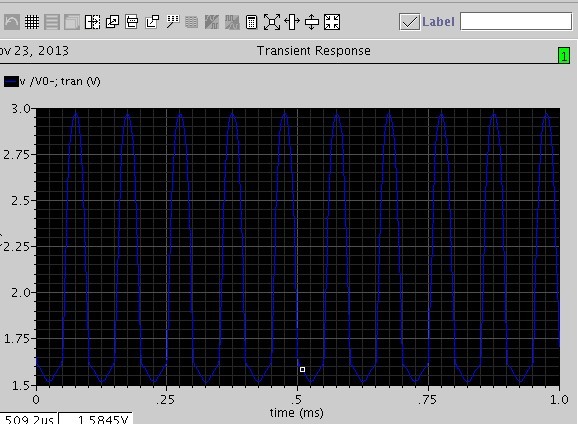

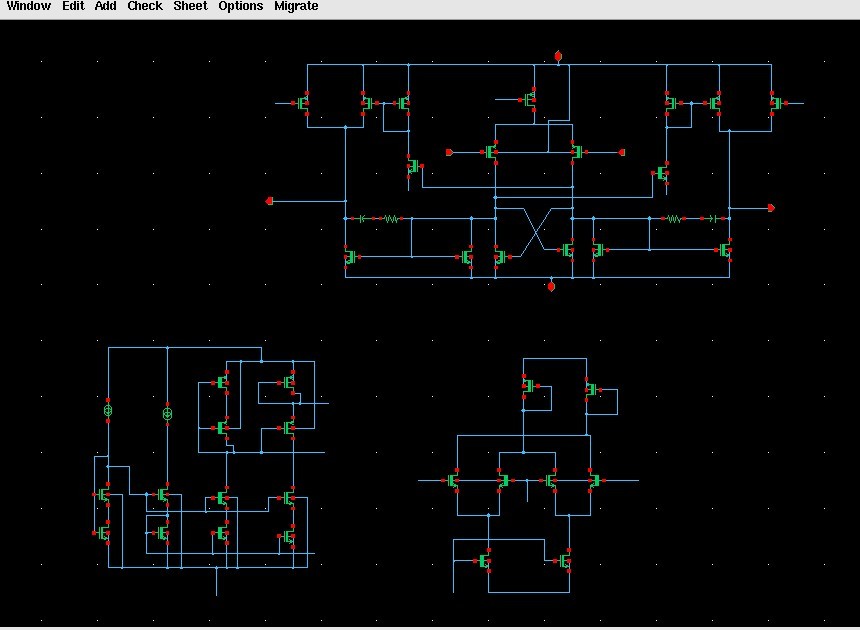

这位兄台,开环做tran是在输入信号很大的情况下没有意义,我的设置是完全能够保证他的管子工作在饱和区,而且现在的问题应该不是有没有意义,就是对于这种情况他出现的原因是什么呢,为什么会这种情况,因为这是一个两级运放,我把每级运放单独仿真的时候,他的输出(都是在相同的开怀条件下)是正常的(见图:正常),但是把两级连接在一起就出现这种问题。

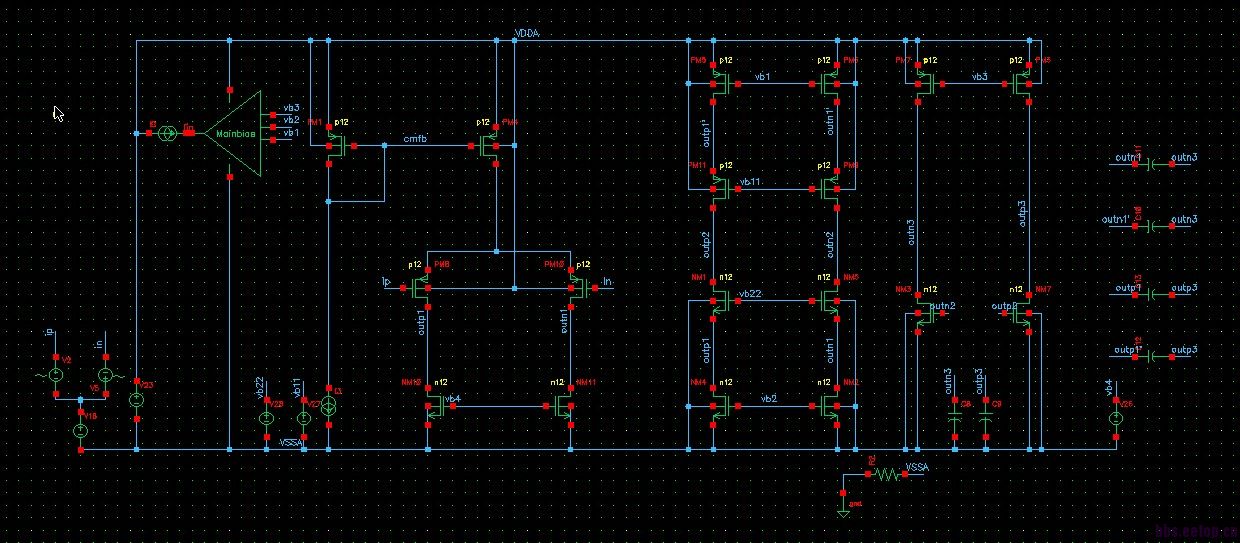

xiexie,我的电路图如下图:电路图所示,仿真条件就是我上面说的运放 89dB,GBW=1.2G。我的输入信号时1mV,10MHz,但是在开环条件下仿真的。有些大神说开环仿真无意义,但是我想因为我给的信号没有使他工作脱离饱和区,所以应该是正确的吧。

刚刚给你回复的掉了,不好意思撒。我的电路图如图:电路图所示。仿真条件就像我在先前说的那样,输入不会使输出失真的。

如果你一定想搞明白tran simulation 为何outp/outn不是fully differential

你分别plot 一下每个点,我猜outp/outn的输出起始点不同,比如一个是从vdd开始,一个从vss开始

DC也许看到outp=outn, 但是tran仿真的初始点并不是DC operating point

至于为何outp/outn不同,仿真器有一定的计算误差,对于高增益的电路,只要有一点误差,最后的结果就差别巨大

BTW: 我为什么告诉你做这件事情没有意义,因为实际应用除了比较器,opamp一般都是闭环应用

比如你的opamp gain=90dB,那么假如你有1mV offset,你在输出端见到~30V,电源是多少,电路还能work?

还有一点你的测试加10MHz sine 你知道opamp这时候gain是多少?这算是3dB带宽还是别的什么?

有功夫在这毫无意义的东西折腾还不如搞搞其它

你图上cmfb悬空了?而且共模反馈放在那里不太好吧。开环仿tran没什么意义,仿个ac不就都包括了。你还是先把电路搭全了再说吧

后来知道了,主要是任何电路都需要建立时间。刚开始给电路上电,所以需要一定的时间来建立。不过真的很感谢你的回答。能顺便问下你,怎么改善输出的thd么?麻烦你了。

尽管没有描述清楚仿真时输入是具体如何加的,但看起来还真是建立期间的状况。如果你能把之前仿真时稳定后的直流偏置点存下来,新仿真时把它load进来再作瞬态仿真,应该就不会有这个问题了。

LZ 你是怎么解决这个问题的呢?我觉得这个不应该是信号建立问题,你的输入又不是一个大的阶跃信号!

电源上电怎么不是大信号?

确实与信号建立时间有关 我做了一个试验,给小信号频率比较低的时候 不存在LZ这种情况 但是小信号频率较高的时候就逐渐有这种情况出现我想请问小编如何解决这种情况?提高建立时间

你仿真用的是op还是powerup?信号上电方式不一样,效果就不一样。如果用preview,肯定不会出现上升的这段时间。

你说的preview 是指什么?我没有用过?指教

hspice里仿真上电的参数。powerup是从电源v=0开始算的,op是从设定的电源电压开始算,preview是从稳定点开始算的。具体你可以查hspice的手册。

我用的cadence 不知道在哪儿设置 我也没有找到!你主要研究什么方向?

哦,我用的是hspice。cadence里的是spectre,不一样,我不熟。我是做器件的。

有个建立时间

能留个联系方式吗?我QQ 717541357以后多交流

我QQ 717541357以后多交流哈

LZ,我做了一个全差分,也遇上了一个奇葩问题,输出电压在1.5V就截止了,怎么调都不行,也问了很多同学,他们也都不是很懂,希望LZ可以帮忙看一下。太谢谢了

谢谢分享