请教DNL/INL的仿真方法

既然是matlab,不妨多取些点,这么抠门干嘛,才取2-4个点 不行

建议每个code上出 100点,整个输入ramp长度 100×2^N

那么只要去看每个code出现的次数减去平均数,再除以平均数,就是DNL

点数越多,精度越高,你用2-4点,少一个点就要差很多

实际测试中码密度测试也会去非常多的点,点越多,置信概率越高

INL就更简单,把DNL 积分起来就可以了,就是累加起来,或者用理想曲线跟实际曲线相减即可

BTW: 啥时候model弄好了,给大家分享一下哦,哈哈

我是2的4次方16个点。谢谢你的建议。

网上有个很著名的matlab toolbox 就可以用来计算

这个论坛上也有

现在已经有了思路,明天我试试看看。不懂再请教!

你现在有?可以共享下不?

已经成功了。

这个Spectre仿真需要花多少时间才能取到这么多码?

1024点DFT通常需要1-2天,这个是100×1024点,不知道要不要100-200天

我目前还没见过在仿INL/DNL的, 完全没有必要, 看看频谱就足矣

呵呵, 所以我这么问.

只是用matlab建模而已。当然不敢用spectre仿真。

如果是理想的数学模型的话,怎么去拿影响DNL和INL的非理想因素呢?是不是要拿计算机的浮点运算误差来玩?

matlab建模肯定会把cap mismatch, gain error, settling error,甚至cahrge injection这些非理想因素加进去的.

记得这里有Razavi实验室用的pipeline matlab system code

考虑到失配的随机性,应该跑个几百次,假设为M次,10位的adc。这时候DNL是一个M*1024矩阵。这时候我们取DNL的时候该怎么取?选取每列最大的DNL作为该码的DNL?这样或许会很苛刻。我试着这样做发现对失配的要求相当苛刻,单位电容面积会达到几百um2

我这里是考量电容失配误差的影响,所以只加了失配进去。

我很感兴趣这里的模型是怎么建的。因为DNL/INL是统计行为,除非你把非理想因素的统计行为写成了量化分析的传输函数表达式,否则是完全得不出真正意义上的DNL/INL的。统计行为的分析确实需要通过统计仿真来得到,而这样做的计算资源是远远不够的。在测试系统上就不同,我们在很短的时间里面可以从测试仪器上得到大量的码流数据,这样的行为我还不知道怎么仿真出来,想请教一下这里面有经验的同行分享一下。

其实我也想过这个问题,但是等我想明白这个东西以后,也懒得去做个Model了

这个问题就类似于实际电路仿真中的montle carlo瞬态仿真,然后测量INL/DNL

那么对应到matlab model中, 你就要给 cap 产生一系列的random offset,

然后基于每套offset值,去做瞬态仿真,提取出该套capacitor 对应的INL/DNL

不同的seed就得到不同的offset值, 比如产生1000套offset 值,然后可以得到1000个INL/DNL

这个东西应该就会有个分布, 看看+/-3 sigma在什么范围

这个就可以模拟类似的实际情况

ps:我比较懒,都是自己手算算,跟实际测下来的match就ok了,你要是有兴趣就应该继续做下去

我对每个码的M组DNL分析了下,基本都在3sigma范围内。这样的话取这M个DNL中的最大值是可行的。我电容失配标准差定为0.4%时,run400次,DNL最大为1.5LSB,INL最大超过2LSB。这个跟预期的差别很大啊。

你做的是什么ADC的model? 0.4%的mismatch显得太大了,是sigma还是3sigma?

所有capacitor的random error都是随机的么?

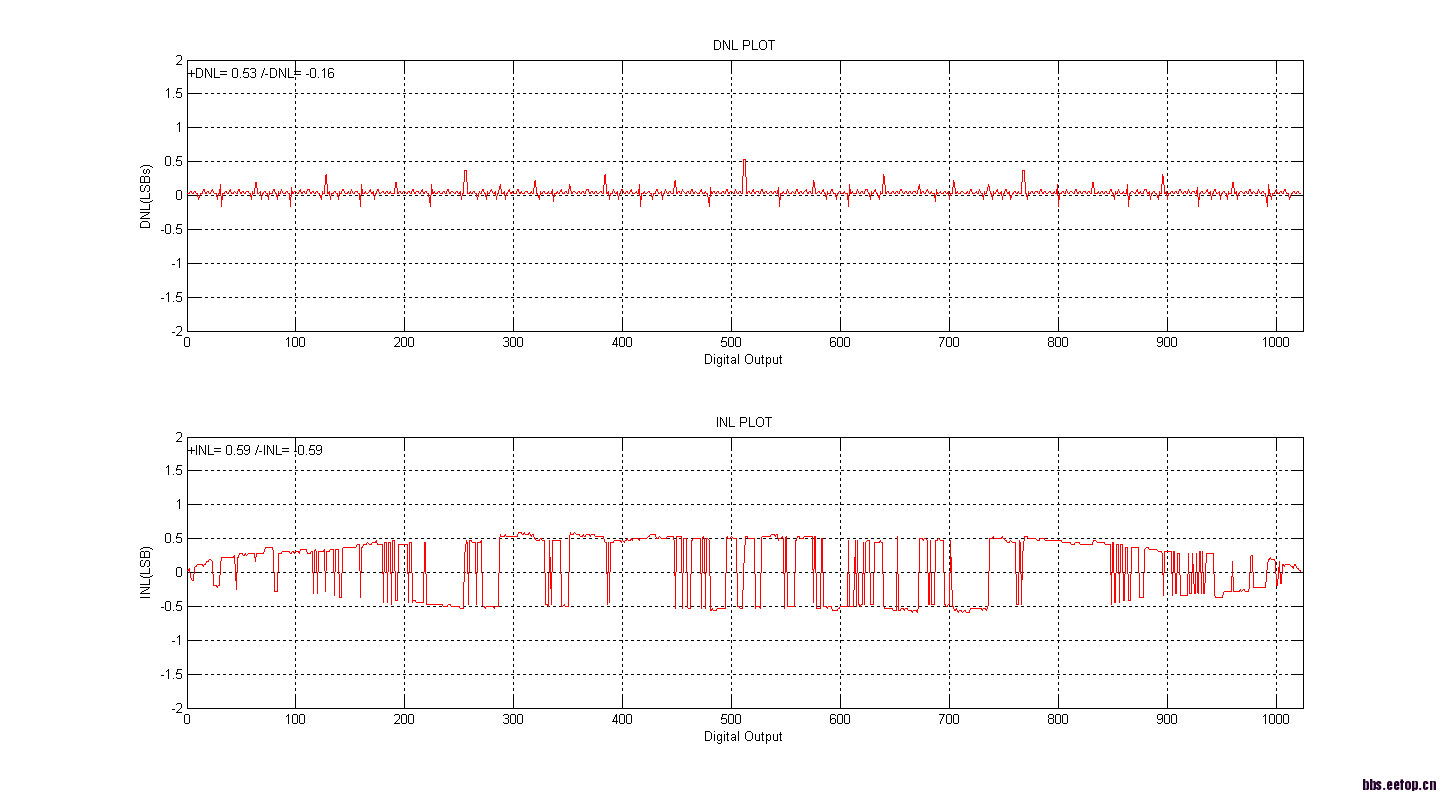

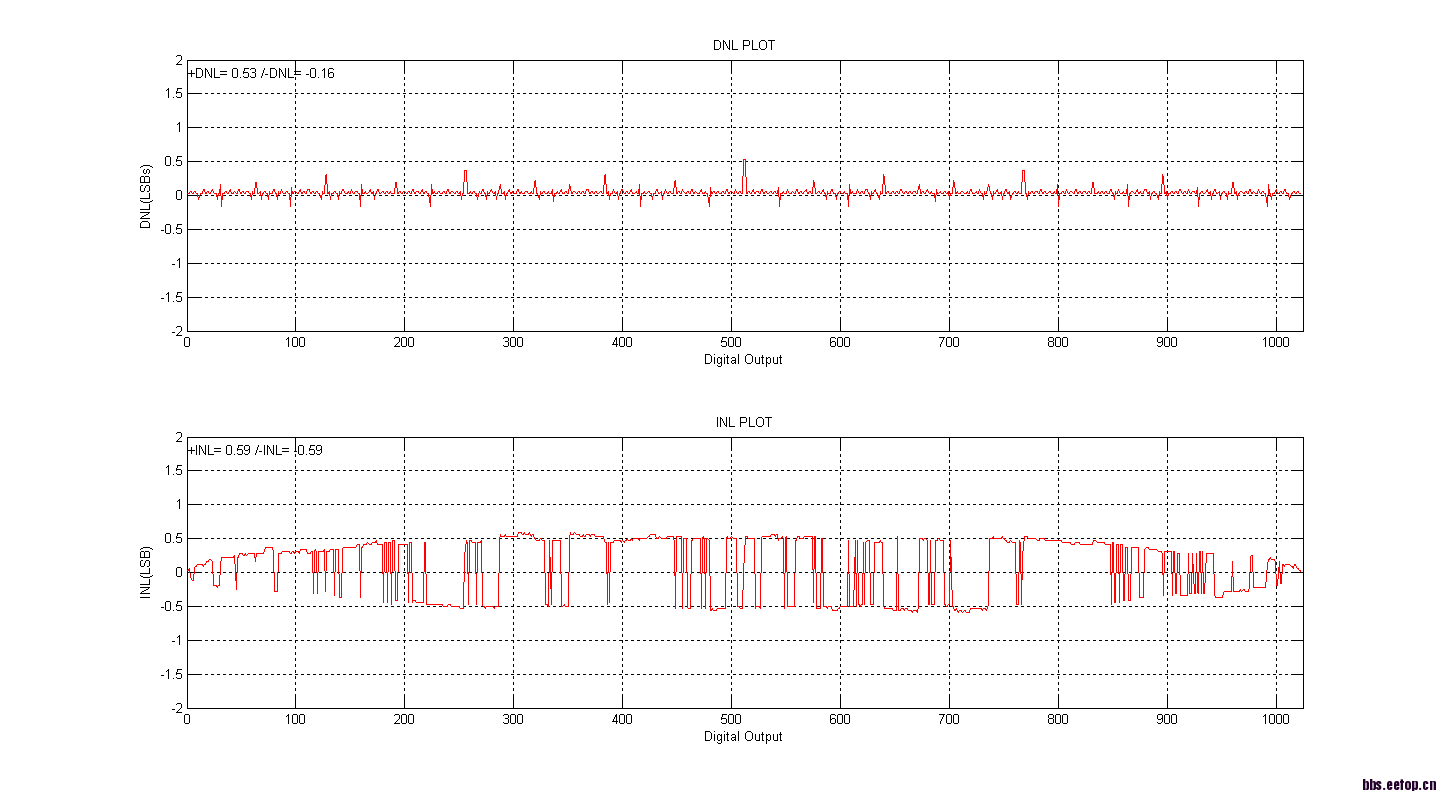

差分 sar adc 电荷再分配型,二进制结构。我已经找到问题所在了,是代码出了点问题。下图是跑1000次的结果,每个码的DNL/INL是取这1000次结果中的最大绝对值。INL是DNL累计的结果。怎么感觉INL的图怪怪的?

兄弟,以后图片搞成.png吧,bmp太大了,手机看,伤不其啊

抱歉,现在可以了,你帮忙看看

好像INL有问题,通常INL不会突变,或者在权重高的位变化比较大,你的图怎么会来回在0附近跳动,再仔细检查电容的随机值或者SAR工作过程搞对没有?

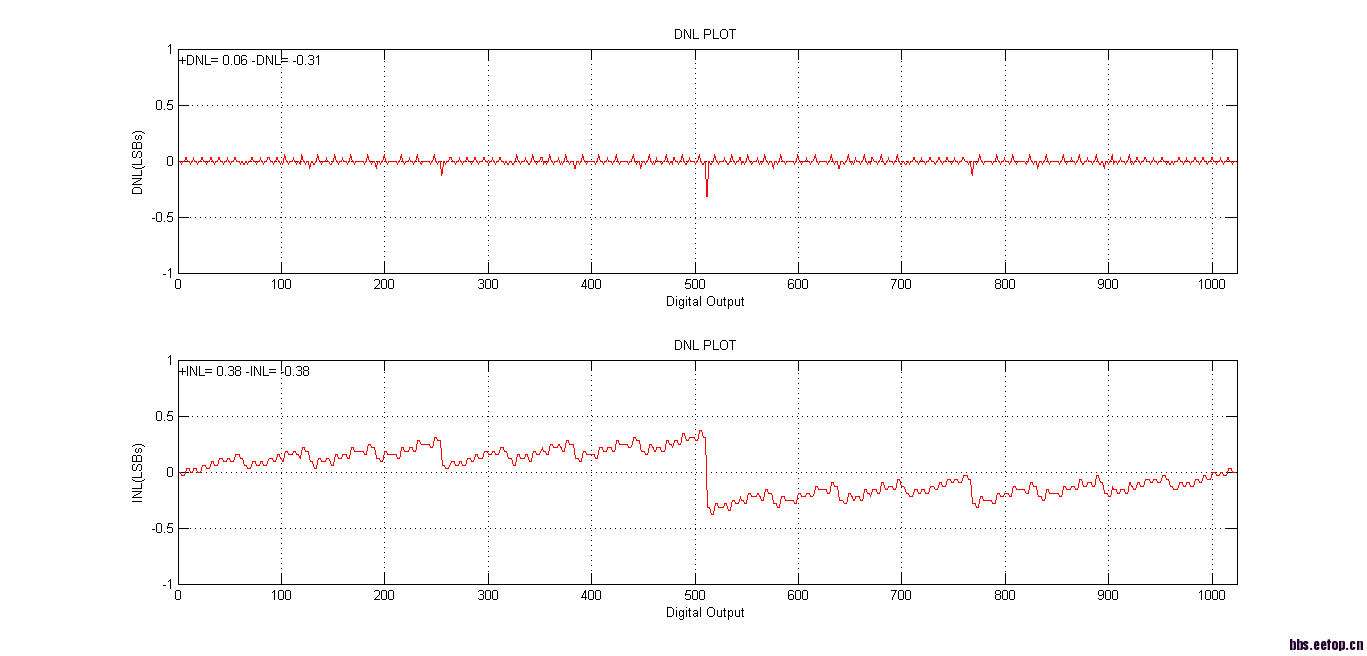

但是这个DNL应该是对的吧?我也很奇怪为什么这个INL会呈现出这个趋势。我给看一个一次的。

我终于明白你在说什么了,哈哈,一次的这个是对的

我没有说让每个code上去1000次里面最大的!因为这样取是不对的

对应一条曲线,表示1个adc,你应该取一个最大的INL/DNL值,然后画成直方图

横轴是 INL/DNL的LSB,纵轴是出现的次数,应该近似于高斯分布

然后看看+/-3 sigma ,或者定一个spec,DNL<+/-0.5LSB, INL< +/- 1LSB

有多少yield

INL好像还有问题,似乎多算了1倍,我看你的DNL在512时候最大,-0.3LSB,但是到INL这里为什么是-0.6LSB了?

按照定义INL是DNL的积分,那么在该点处的INL变化就是DNL值

你的意思是只要把每次ADC最大的DNL/INL取出来做一个统计就可以了?而不用去考虑每个码的情况?

不能比较不同的adc每一个code处的INL/DNL,因为最大值可能出现在不同地方,最后性能却差不多

嗯。我就是把每个ADC的最大DNL/INL取出来做一个统计分布。同时也对每个码的DNL/INL的标准差和均值变化做了一个统计。你可以看看图,提提意见。

我想了一下,如左上DNL max的分布,直观地想,这个么多sample的DNL max 应该不会是在0LSB出现概率最高,反而是概率接近0

但是我还没想明白这个分布是怎么产生的

对于std DNL来说,不需要仿真都可以知道,DNL只跟对应权重的cap的sigma有关,那么必然是512时候最大,然后以0.707的比例递减,

分别在256/768, 128/384,640/896 ...等权中上。 但是,通常在实际测试,并不是在这些code上的DNL会更大

平均步长的标准差也是完全由电容的误差决定,没有见有谁用过

我觉得如果瞬态能做出THD和SFDR,也许会有用,能看到这些sample的total harmonic distribution还是有意义的