流水线ADC噪底过大

看不到图,你测试的点够不够多? 为何你说搭了14位又说理想只有12.8,到底哪个是你的模型

看不到图啊?

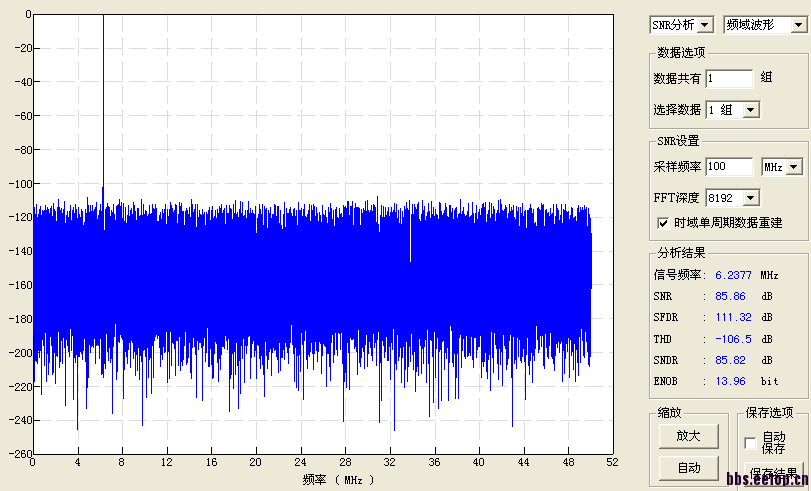

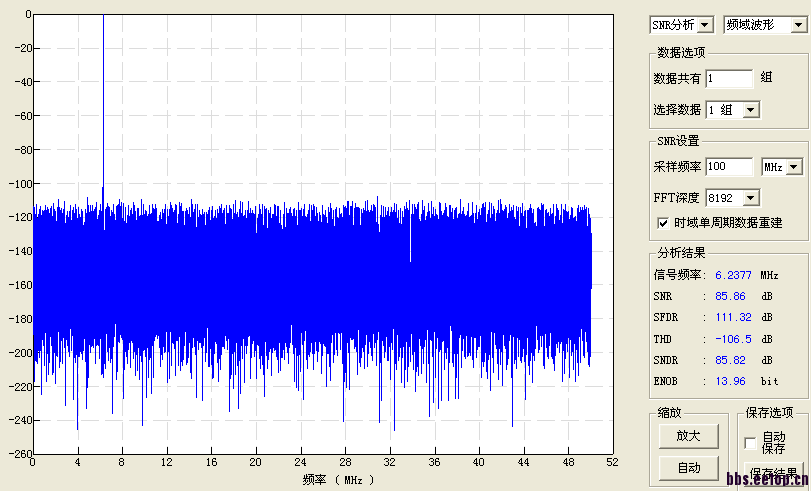

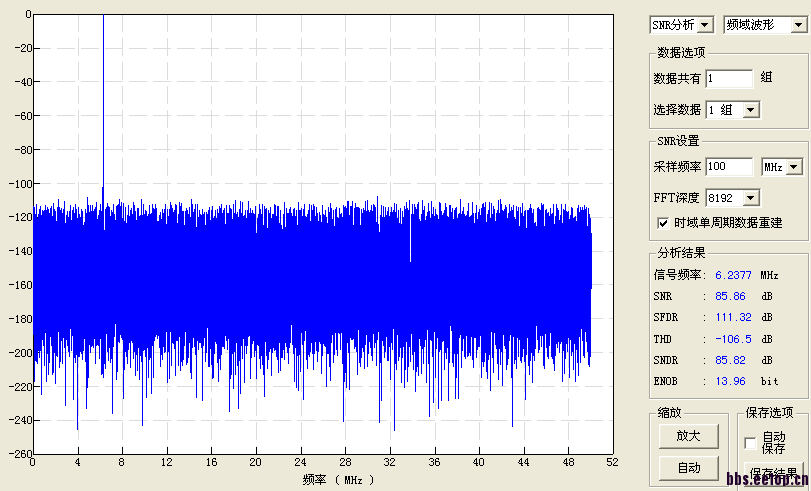

,哦不意思,第一次上传图片没上传好。这个是我用simulink建的模型得到的结果。后来我又仔细检查了一下,把输入信号电压改成满幅信号后,采样8192个点,采样频率100MHz.有效位数提高到13.96位。后来又仔细检查了好多遍,都还没解决,怎样提高到14位呢。我采用的7级流水每级2.5位,最后一级是2位,经过延迟对齐后错位相加得到十四位数字输出。请指点迷津啊。再请教一个小编大哥一个问题,我看到一些资料上说测试ADC的输入信号fin=Fs*M/N.要满足这个关系。我的ADC就是根据这个模型来测试的,得到了上述结果。但是这个时候,传输曲线的结果又不对,当采用较小的输入信号频率时,传输曲线正确,但是得到的ADC的有效位数和SFDR结果却很差(只有4点几位和30多dB)。请问为什么会出现这样的情况?先谢谢小编大哥。

不知道为啥,我把图片上传了,完成后还是没有图片。

多谢大哥。图片我上传了,如图

只有仿真的时候能够符合fin=Fs*M/N的条件,测试的时候要按datasheet中的频率来,结果要加窗

频率小SFDR差可能是你原来频率大谐波在带外没算进来,频率小谐波在带内所以差,最好给个准确数字大家好分析,大小之类的词不好说。

图还是不行

SNR当然和信号幅度有关系咯,需要归一化到 fullsacle

信号幅度小,但是noise是不变的,SNR自然就小了

谢谢小编。我的采样频率为100MHz.理想输入信号频率为6.25MHz.满幅为:2V(-1~1V).实际输入频率fin=(100*511/8192)*1e6Hz.得到SNR=85.86 SFDR=111.32 SNDR=85.82 ENOB=13.96.在这种情况下传输特性曲线很差。不知是什么原因?。

谢大哥的指点。

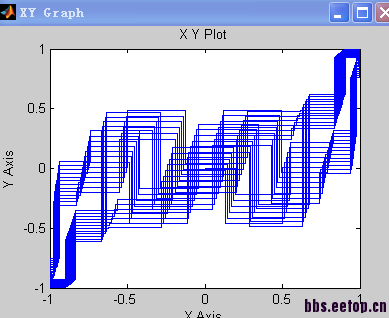

曲线很差?有图吗,是不是没校准

这是得到有效位数13.96位时的第一级的传输曲线,

虽然不知道你这么多曲线代表什么,你这个图没看到什么问题,工作正常的

谢谢小编

不太懂· 正在学习当中,怎么着手流水线ADC都不晓得