探讨使用transistent noise仿真 jitter noise

时间:10-02

整理:3721RD

点击:

今天尝试着仿真jitter,因为以前用过transistent noise分析kT/C noise,这次也用同样的方法。

只是我个人的观点,希望大家能帮我看下这样对不对。

首先是jitter noise的定义,时钟抖动jitter可分为

1、周期抖动(period jitter),即rms(tn+1-tn-T)

2、周期间抖动(cycle to cycle jitter),即rms[(tn+2-tn+1)- (tn+1-tn)]

3、长时间累计抖动(time interval jitter),即rms(tn+1-nT)

ADC一般关心的是第三类噪声,

这里以一个反相器为例,给1GHz的理想时钟,测一下经过这个反相器之后的jitter noise

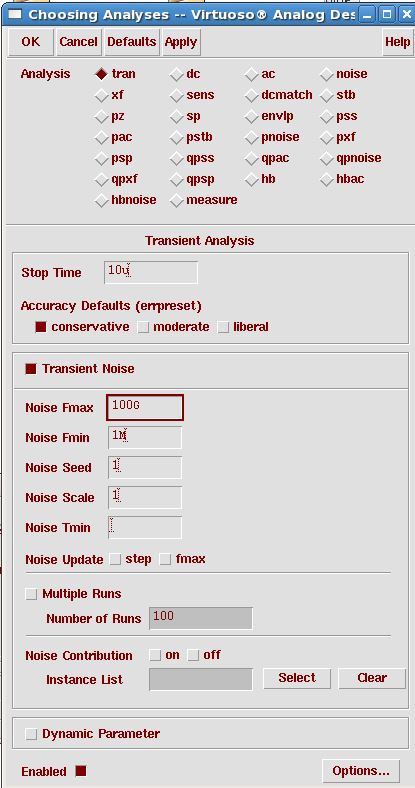

这里要设置的有

stop time ——取得长点准确点

fmin—— fmin>1/stop time

fmax—— 这个值越大越准确,但会让仿真时间变长(之前看到有帖子用fmax=fclk,我认为是不对的啊,噪声是在无穷的频带积分的——虽然因为电路自带滤波会让远处的噪声被滤掉,但fmax取大一点会更精确)这个多试几次就知道哪个值合适了。

这里我也是按仿真kT/C noise的经验,各位大神能否说说fmax应该怎么取。

seed—— 随便给个正整数

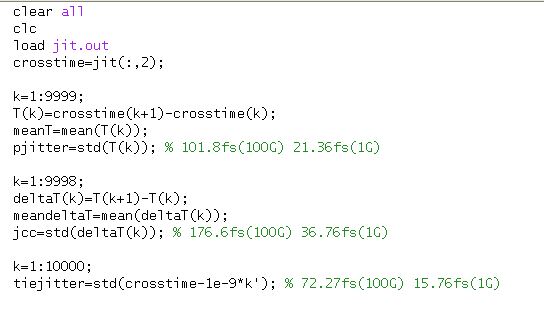

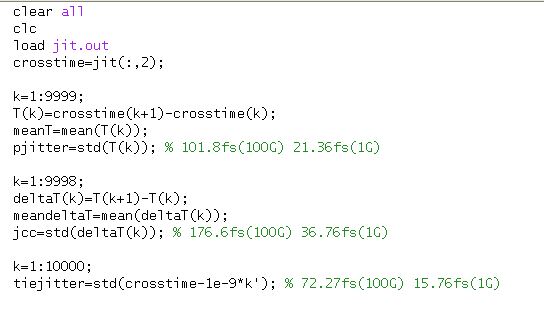

然后是caculator写好表达式用ocn语言导出,这里要注意小数点后多取几位,不然结果不精确

然后导入matlab处理一下

问题来了,fmax=1G和fmax=100G仿真出来的结果相差很多,fmax=100G的时候,jitter noise有100fs左右,一个反相器 jitter noise有100fs,这也太夸张了吧,求教俺哪里弄错了

谢谢您的回复,我再去看看jitter是怎么产生的,看来必须要了解原理,不能盲目仿真。

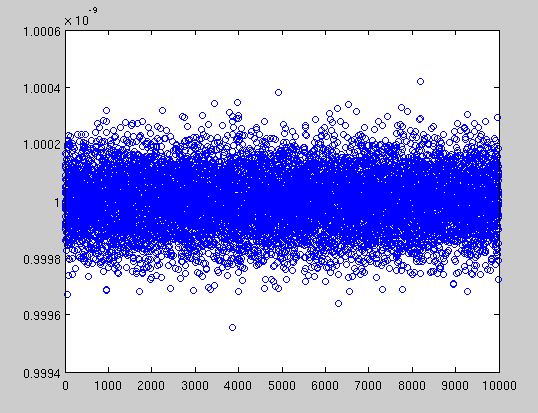

横坐标是cycle数,纵坐标是每个cycle的时长。

只是我个人的观点,希望大家能帮我看下这样对不对。

首先是jitter noise的定义,时钟抖动jitter可分为

1、周期抖动(period jitter),即rms(tn+1-tn-T)

2、周期间抖动(cycle to cycle jitter),即rms[(tn+2-tn+1)- (tn+1-tn)]

3、长时间累计抖动(time interval jitter),即rms(tn+1-nT)

ADC一般关心的是第三类噪声,

这里以一个反相器为例,给1GHz的理想时钟,测一下经过这个反相器之后的jitter noise

这里要设置的有

stop time ——取得长点准确点

fmin—— fmin>1/stop time

fmax—— 这个值越大越准确,但会让仿真时间变长(之前看到有帖子用fmax=fclk,我认为是不对的啊,噪声是在无穷的频带积分的——虽然因为电路自带滤波会让远处的噪声被滤掉,但fmax取大一点会更精确)这个多试几次就知道哪个值合适了。

这里我也是按仿真kT/C noise的经验,各位大神能否说说fmax应该怎么取。

seed—— 随便给个正整数

然后是caculator写好表达式用ocn语言导出,这里要注意小数点后多取几位,不然结果不精确

然后导入matlab处理一下

问题来了,fmax=1G和fmax=100G仿真出来的结果相差很多,fmax=100G的时候,jitter noise有100fs左右,一个反相器 jitter noise有100fs,这也太夸张了吧,求教俺哪里弄错了

transistent noise是什么仿真方式?

个人理解,“给1GHz的理想时钟,测一下经过这个反相器之后的jitter noise”,这么做等于是把反相器的噪声(1/f和沟道噪声)搬到1G的频带内,再在频带内积分获得输出噪声吧,这么做有什么意义么。

关注下关注下

少了一张图..不会发图..

谢谢您的回复,我再去看看jitter是怎么产生的,看来必须要了解原理,不能盲目仿真。

横坐标是cycle数,纵坐标是每个cycle的时长。

我试着仿真了一下,通过我一楼说的仿真方法发现jitter noise的值跟时钟频率几乎没有关系,