求助:bandgap怎么加启动电路

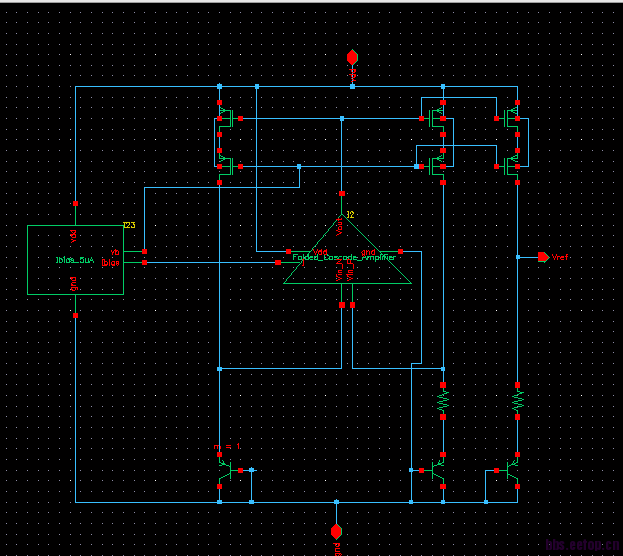

这是我设计的bandgap电路,怎么加启动电路啊 ,怎么都学不会啊,在哪加?真心求助。

这是我设计的bandgap电路,怎么加启动电路啊 ,怎么都学不会啊,在哪加?真心求助。

怎么木有人帮忙啊

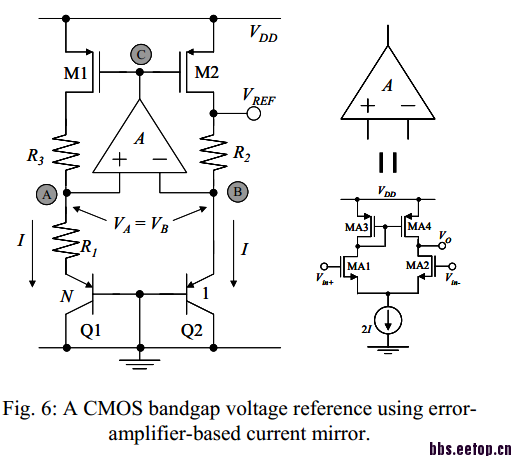

在运放输入节点注入电流,使环路利用正反馈建立起稳态工作点,之后检测并利用vref电压关断启动电路对环路中节点的电流注入。

在你运放输出端加个cap作为loop补偿。然后启动电路加在运放输出端也就是你电流镜端,用一股比较小的电流拉这个gate段,使得整个loop摆脱零简便点。 需要注意的是运放启动后要去掉这股电流。

你可以用电流端多分出一路来,当电路摆脱零简便点后,镜像出来的电流能把这股startup电流干掉

There are quite some ref start circuits in Paul Grey and Razavi's book

是有 可是不知道加在具体电路的哪里

呵呵 不是也别明白 第一次做这个 还是要真心的感谢

看看,路过!

很明显。小编很用心呢

不知道运放怎么做的,如果运放的电路零电流的简并点的话,运放也要启动电路,可以把bandgap和运放的startup做在一起,搜搜论文吧,很多的。像你这个电路有可能起不来的情况就是最上面的pmos管开始时不通,你就可以开始加一个低电平在栅上,等到电路启动了,就会产生一个bandgap的电流(PTAT),这个电路再回去把你的启动电路关掉就OK了。

用倒比管子做启动电路

运放和三极管的集电极都要做启动电路,抓哟是要给三极管注入一定的电流,返过来三极管导通后还要关断你的启动电路

他都有bias了,不需要启动电路了

学习学习!

顶小编,学习了。

路过看过!

小编很用心!

学习受教呀!

这个真心不会啊

Due to the relatively high input capacitance (compared to

otheranalogtodigitalconverterarchitectures),SARADC's

maximum speed is dominated by sampling time of the sample

andholdstage.Thesecondlimitingfactoriscomparator

decision, as small differences in input voltage, namely less than

1 LSB, must be resolved within one clock period.

decision, as small differences in input voltage, namely less than

1 LSB, must be resolved within one clock period.

请问一下bandgap为什么会需要启动电路?电流为0的工作状态是为什么会存在的?能不能详细分析一下》》》》一般给的资料上是画了一个图,两个交点,一个(0,0),一个operation点。可是还是不是很明白

比如这个电路,分析一下具体工作的时候为什么可能会稳定在零电流

ibias提供的偏置,而不是通过基准源产生的参考电流

C= VDD, A/B=GND,这是一个稳态,电流为0;

弄一路電流出來,給電阻性負載即可

学习学习

pmos bias & pmos cascode