关于运放的系统失调电压

以下假定为单电源5V的供电系统。

运放的失调电压分为随机失调和系统失调,随机失调是由于工艺偏差和版图的失配导致的,是不可完全消除的;而系统失调是在没有随机失调的情况下,由于电路的结构导致的,当输入电压为0.5VDD时,输出电压不为0.5VDD。系统失调定义为:VOS=(0.5VDD-VO)/AV。(理想的无随机失调的情况下)

系统失调是可以通过电路结构的优化消除掉的。

问题1:系统失调一定要消除掉吗?有些电路中故意会做得存在系统失调会更好吧?

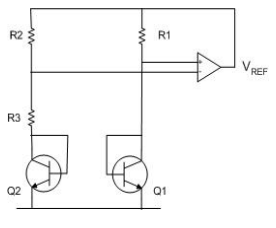

例如在带隙基准电路中,以经典的一个运放+三个电阻+两个PNP管的带隙基准为例,其输入端接在PNP管的发射极端,输入的直流偏置点约为0.7V,而输出接电阻,输出基准电压VREF,约为1.25V。

对于这样的一个应用电路的运放,是不是有意的引入系统失调,将其共模输出电压设计在1.25V更好呢?还是要设计在0.5VDD呢?哪一个更好?如果说共模输出电压设计为0.5VDD更好,那么将输出共模设计在1.25V有什么问题呢?

而我们所说的失调电压对带隙基准精度的影响都是指的随机失调吧?系统失调对带隙基准的精度有影响吗?输出共模电压有偏差,但只要环路工作时,运放的两输入端电压精确相等,就不会导致带隙基准的漂移。

问题2:另外,随机失调在后仿真时怎么仿呢?一般版图作得对称性很好,提取参数后也很难仿出随机失调电压的。是不是可以把差分对管一个以fast模型,一个以slow模型来仿呢?或者有其它更好的办法吗?

怎么没人回复呢?自己顶一下。

帮顶。

简单说说我的看法

1 同意 “对于这样的一个应用电路的运放,将其共模输出电压设计在1.25V更好“。

2 系统失调会影响初始精度,特别是Va比较小的时候。

3 说到“有意的引入系统失调“,问题在于是不是可靠的。个人觉得这里process varation

和mismatch的影响会大得多。一般的做法是把Va做的足够大,mismatch什么尽量减小,也有一些

从电路结构上考虑。

4 随机失调可以用monte carlo法来仿真,有些foundry例如TSMC会给Vt, size的mismatch数据,

根据这些数据作仿真,可估算输出电压的分布。(可惜我也是纸上谈兵,实际也没做过。)

这个问题不太懂,不能帮你了

谢谢各位的帮忙,特别感谢_Ryu。

我这几天也在看monte carlo仿真,不过貌似需要工艺支持,不知道根据工艺角数据自己能否推算出高斯分布函数。这块现在还没弄明白呢。有知道的大侠说说呀!

另外_Ryu提到减小mismatch的方法是把VA做得足够大。我这两天也想过,不过这个方法好像行不通。因为失调主要来源于差分对。VA越大,输出失调就越大,输入失调一直是不变量。输入失调的仿真方法是输入失调=输出失调/VA,但输入失调来源于输入端,所以与增益无关。

“输入失调的仿真方法是输入失调=输出失调/VA“

这样考虑应该可以的。

1,关于系统失调,VA增大失调减小,这一点相信你也是同意的。

2,那么对于例如mismatch引起的失调,直觉我觉得VA大是有好处的。不过,不知道你又没相应的仿真结果,例如人为加入一个小的mismatch(size or Vth), 改变VA,看看输入Vos是怎样的。

好,谢谢!

[table=98%]

[tr][td]

1、关于系统失调,LZ说是由电路的结构引起的,不同的运放结构导致不同的系统失调?OTA和折叠式共源共栅结构的失调电压不一样?我只是不明白,电路结构中的哪些回产生失调呢,LZ说是差分对引起的,难道还是工艺角?这岂不是又回到了随机失调了?....只是不懂 ,所以请教下。

2、还有就是基准电路中的运放的系统失调应该不是有意引入的吧,1.25V只是恰好产生这么大吧,如果没有失调可能会是另外一个值,只要这个值足够稳定。

3、我们平常所指的失调电压是指随机失调?好多地方说通过一系列方法来减小失调的影响,像增大△VBE,难道这只是用来抑制随机失调的影响的?我觉得系统失调和随机失调应该都会对基准的精度产生影响吧,不知道对不,请指点一二

4、系统失调的仿真办法:是通过把运放接成BUFFER的形式,然后看输出电压和输入电压的差值,即输出失调电压,然后用输出失调电压除以运放的增益,从而得到输入失调电压?系统失调可以通过增大增益来减小?这个应该不对吧

1、LZ的意思好像是对于系统失调来讲,VA增大是行不通的,因为输入失调电压是有电路结构引起的,也就是说输入失调电压是不变的,那么根据“输入失调=输出失调/VA“可以得出,这样做只会增大VA。 2、不过你所说的增大VA在很多电路中,是这样做的,但是应该不是你说的减小输入失调,在基准那个电路中,应该是为了使运放的两个输入端电压相等,是跟据负反馈来说的,增益越大,这两个电压差值越小

当然这也是我随口说的,不知道对不对,还望指教

PS:我也想问下,那个输入失调电压公式哪里来的是对的吗?仿真方法是把运放接成BUFFER,在输入端加一个共模点电压,然后算出

|Vout-Vin|即输出失调电压,再将输出失调电压除以VA得到输入失调电压?就是说直接仿真出来的那个差值是输出失调电压而不是输入失调电压

?

学习了

没有什么实质性的东西啊

我想问问输入失调电压过大时怎么回事?我的增益有90dB

monte carlo仿真只是玩玩设计人员的,没有什么大作用的。

系统失调对于差转单电路来说是无法避免的,这是有结构的不对称引起的

随机失调是由于process和mismatch引起的,可以将输入对管的Vgs-Vth减小,将p和n共源管的Vgs-Vth增大,这样有助于减小随机失调,至于增大VA有减小失调的趋势,但不是绝对的,在这个概念上我也拿不定,增大VA的确能减小输入端的压差,但是加上失配仿真的话,未必VA越大愈好。

你所说的仿真问题,那个可以参见ALLEN第6章上有

大家对BETA值是杂考虑的,我面试的时候被问到了,有点没考虑好,感觉就没影响,而且拉杂为上11.5题的答案感觉也错了。

你是xd的吧

学习了!

正在看,小编这个问题解释的很好

学习学习