请教全差分闭环运放的STB仿真问题

时间:10-02

整理:3721RD

点击:

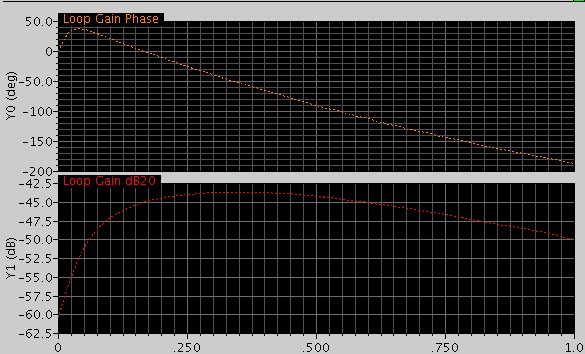

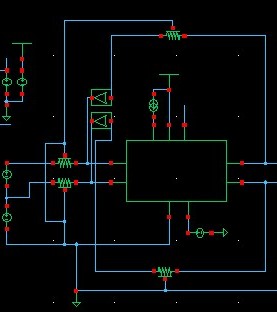

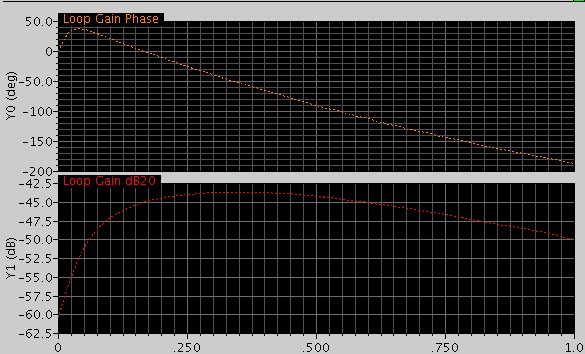

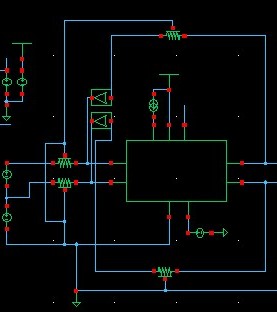

在仿真全差分的电阻反馈闭环运放时,在电路反馈回路中加入cmdmprobe,仿真stb,plot的波形很奇怪增益直接是从负的开始,不知道是为什么?是仿真方法不对,还是这就说明闭环系统不稳定?

运放开环仿真的时候相位裕度有78deg,但皆成电阻反馈的闭环形式就变成这样了……

还请大家多多指教

[img]file:///C:\Program Files\Tencent\QQ\Users\1017253773\Image\[R[RJZN7}HB)PECAVCPD$H9.jpg[/img]

运放开环仿真的时候相位裕度有78deg,但皆成电阻反馈的闭环形式就变成这样了……

还请大家多多指教

[img]file:///C:\Program Files\Tencent\QQ\Users\1017253773\Image\[R[RJZN7}HB)PECAVCPD$H9.jpg[/img]

看一下闭环静态点对么?

直接仿真DC吗?仿过了,所有管子都在饱和区,且输出的共模电平就是所需要的1/2VDD……我还有两个疑惑:一是开环仿真的相位裕度不能说明运放接成闭环也是稳定的吗?不是说开环相当于反馈系数是1时的相位裕度,这种情况是最恶劣的,如果能满足相位裕度,能否说明闭环系统也能稳定?

二是开环仿共模反馈环路的相位裕度,也是足够的,它能说明运放在闭环使用的时候共模反馈环路还是稳定的吗?

1. 相位裕度的本质。

闭环传递函数Gopenloop(s)/(1+Hfeedback(s)*Gopenloop(s))的分母不会出现0点

如果你相位裕度是在Hfeedback=1的时候看的话,你再把gain曲线乘上反馈系数在看

通常是看Hfeedback(s)*Gopenloop(s)的开环而非Gopenloop(s)

2. 开环的时候反馈电路作为负载带上了么?

顶顶!

断点位置有问题

断点位置有问题

先看看open loop对不对吧。stb仿真应该跟断点位置没有关系的,只要在loop里面就行。

断点错误

cmdmprobe 设置为-1