CPPLL 仿真后控制电压摆动太大

时间:10-02

整理:3721RD

点击:

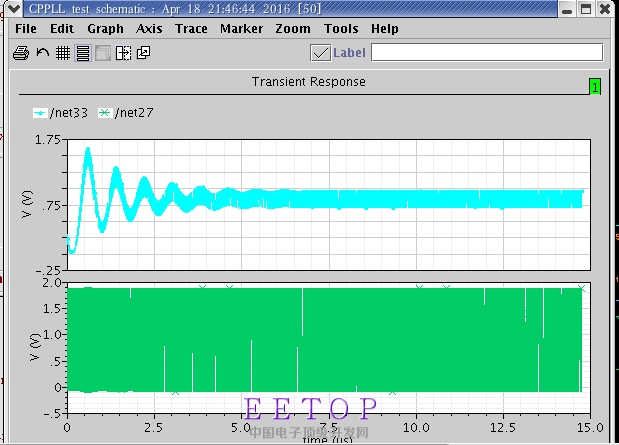

第一个图像是我最后tran仿 然后maxstep设置为2p出现的波形,

现在不太清楚改修改什么地方。

Icp=40uA N=30 Klc-vco=199Mhz/V

R=71K C1=1.558p C2=0.2096p

VCO是2.5GHz

环路带宽是 25pi/3 M=26M fref=2.5G/30=83.3333MHz不好意思 说话有点大喘气,求大家帮忙看看我的问题是什么

带宽太大,高频噪声压制不住

谢谢你的回答,我的fref=83M带宽取的是w=83/20*2pi这样还需要再小一点吗?

还是说我需要增加N,让fref变小,从而带宽也减小吗?

谢谢

小编,你指的是控制电源稳定之后的glitch吗?

我是觉得基本都没稳定。一直在波动,读别人的论文都是细细的一条曲线,我的抖动太大了。

感觉波形的包络已经稳定了,你看看抖动的周期是不是与电荷泵充放电一致。如果一致,那可能loop filter参数不是很合适。电容会不会太小了?

小哥,本来不想回复的。你都不知道自己想要什么。带宽是你需要多少settling。

你要根据开环函数,Zeta,Wn,来确定你的带宽,phase margin.

谢谢帮助,我再读读书

谢谢你的帮助。选完带宽之后计算出来的参数,我也觉得电容小。

现在在重新考虑带宽的问题。

C1/C2=7.4 --> phase margin would not be ok.

Lower your R, increase your C2 to minimized your ripple.