运放设计求助:共模反馈电路中,这个VCM是什么?

时间:10-02

整理:3721RD

点击:

【10】CMOS模拟集成电路设计与仿真实例——基于Cadence ADE

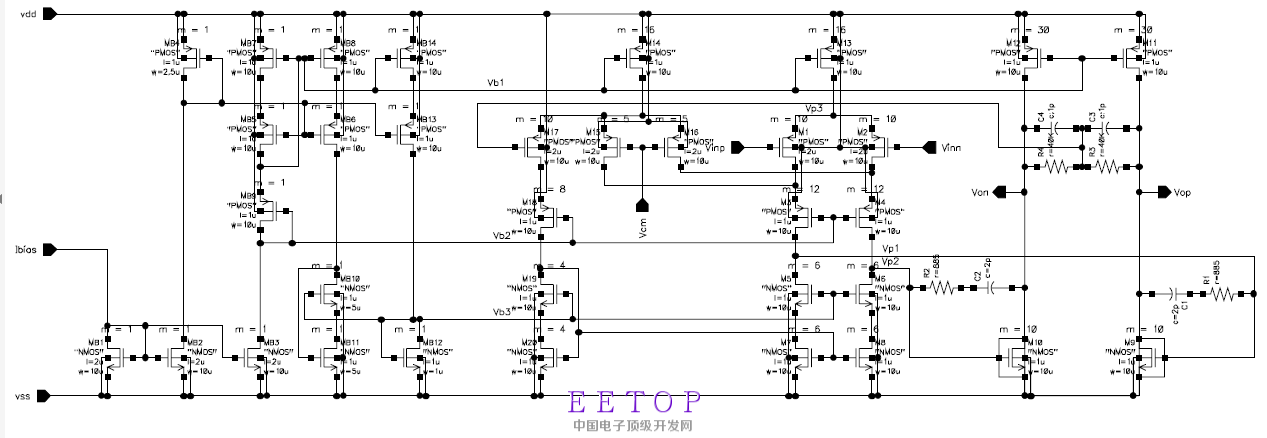

这本教材中运放采用如下电路结构:

后面说采用的包含共模反馈的总电路是这样的:

我有两个问题:

1、第一图中的Vcmfb应该就是第二图中的Vcmfb,可是第二图中并不是这么连的,为什么?

2、第二图中的Vcm是什么?外接的一个固定偏置?反馈的原理是怎么样的呢?

请高手指教!

谢谢!

按照你的电路我仿真了,功能基本实现,但是增益只有80多dB,与文中的115dB相距甚远,请问是什么原因,我感觉偏置出了点问题,你的偏置明显与他的不一样,但是按原文的更是不行,有高手指点下这个偏置电路?

这本教材中运放采用如下电路结构:

后面说采用的包含共模反馈的总电路是这样的:

我有两个问题:

1、第一图中的Vcmfb应该就是第二图中的Vcmfb,可是第二图中并不是这么连的,为什么?

2、第二图中的Vcm是什么?外接的一个固定偏置?反馈的原理是怎么样的呢?

请高手指教!

谢谢!

replica

完整结构应该是这样子的

赞一个

哦哦哦

非常感谢!我再仔细看看!

能发Cadence下project?谢谢!我的邮箱52306080@qq.com

还不错。

这个例子就是唐长文那个文档中的例子 可以参考那个运放设计文档

按照你的电路我仿真了,功能基本实现,但是增益只有80多dB,与文中的115dB相距甚远,请问是什么原因,我感觉偏置出了点问题,你的偏置明显与他的不一样,但是按原文的更是不行,有高手指点下这个偏置电路?

谢谢!能介绍下偏置电路为什么如此设计?