pll锁相环的VCO控制电压抖动问题

时间:10-02

整理:3721RD

点击:

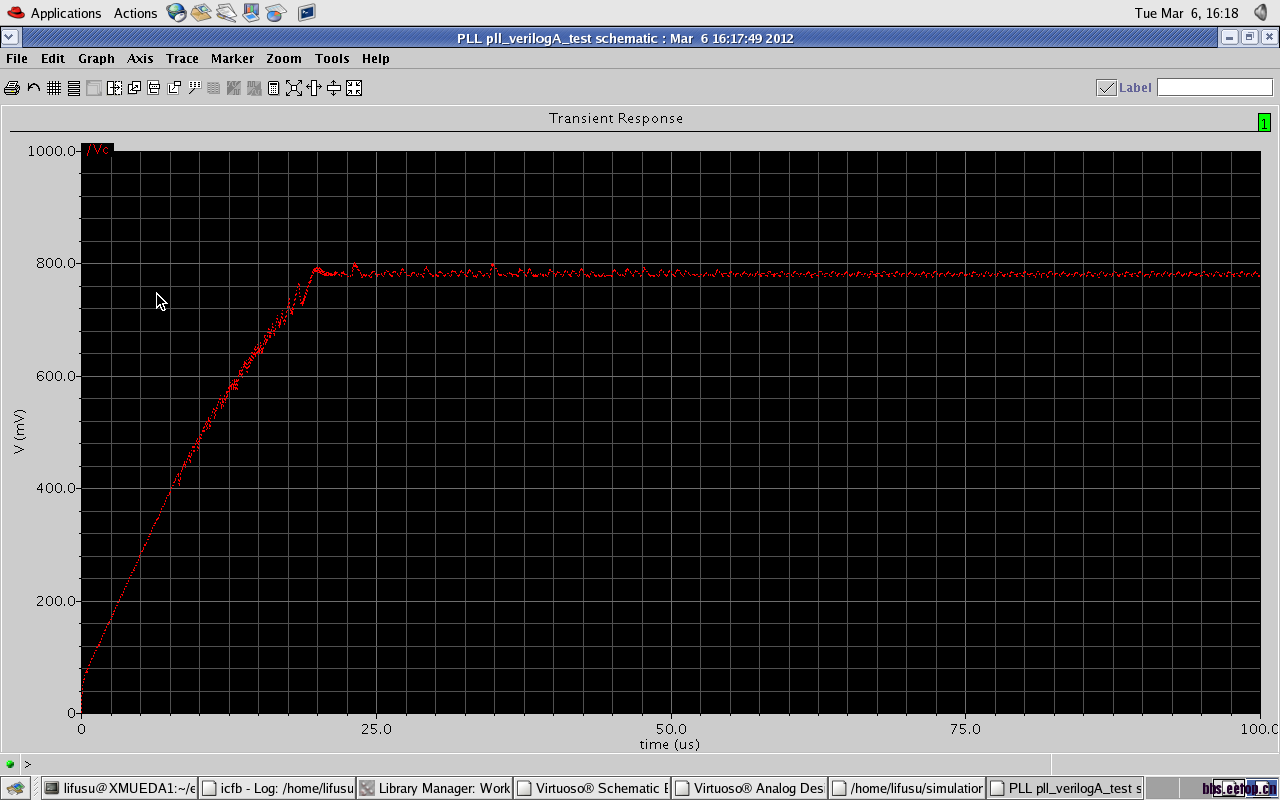

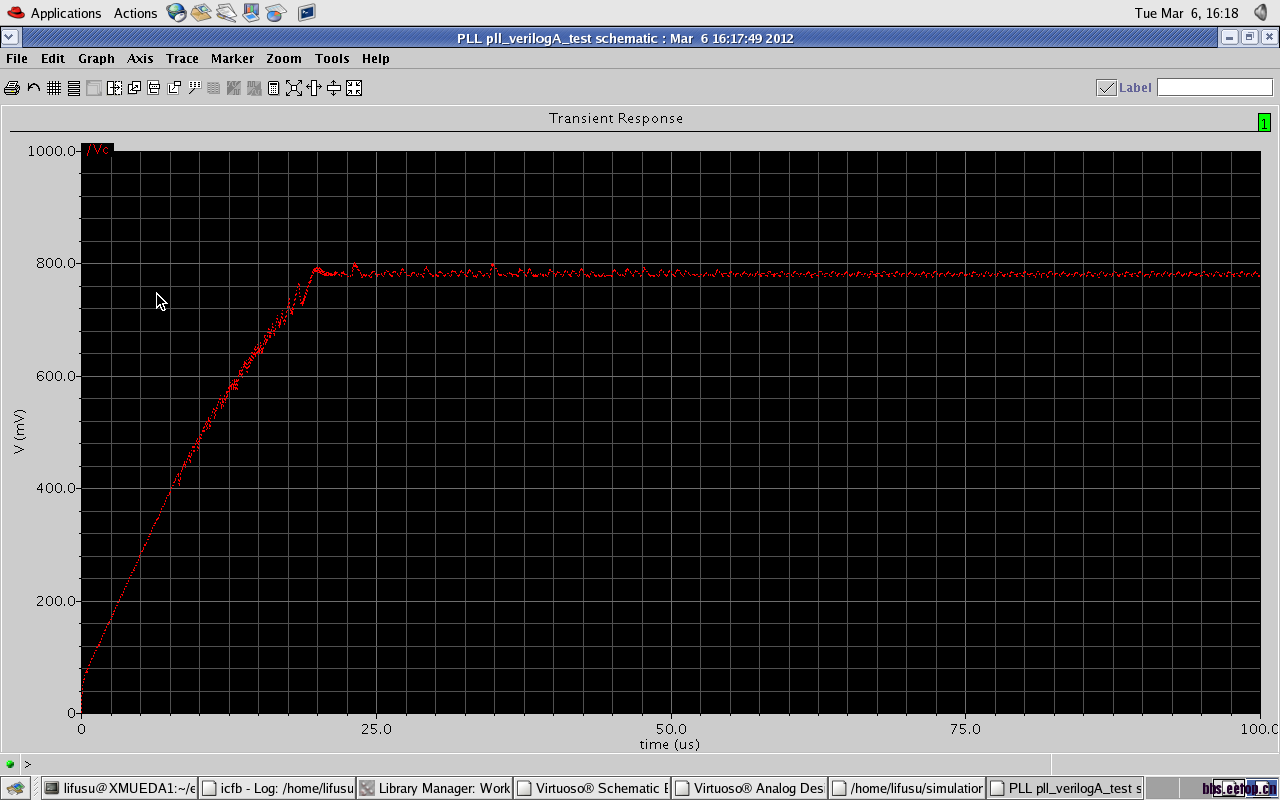

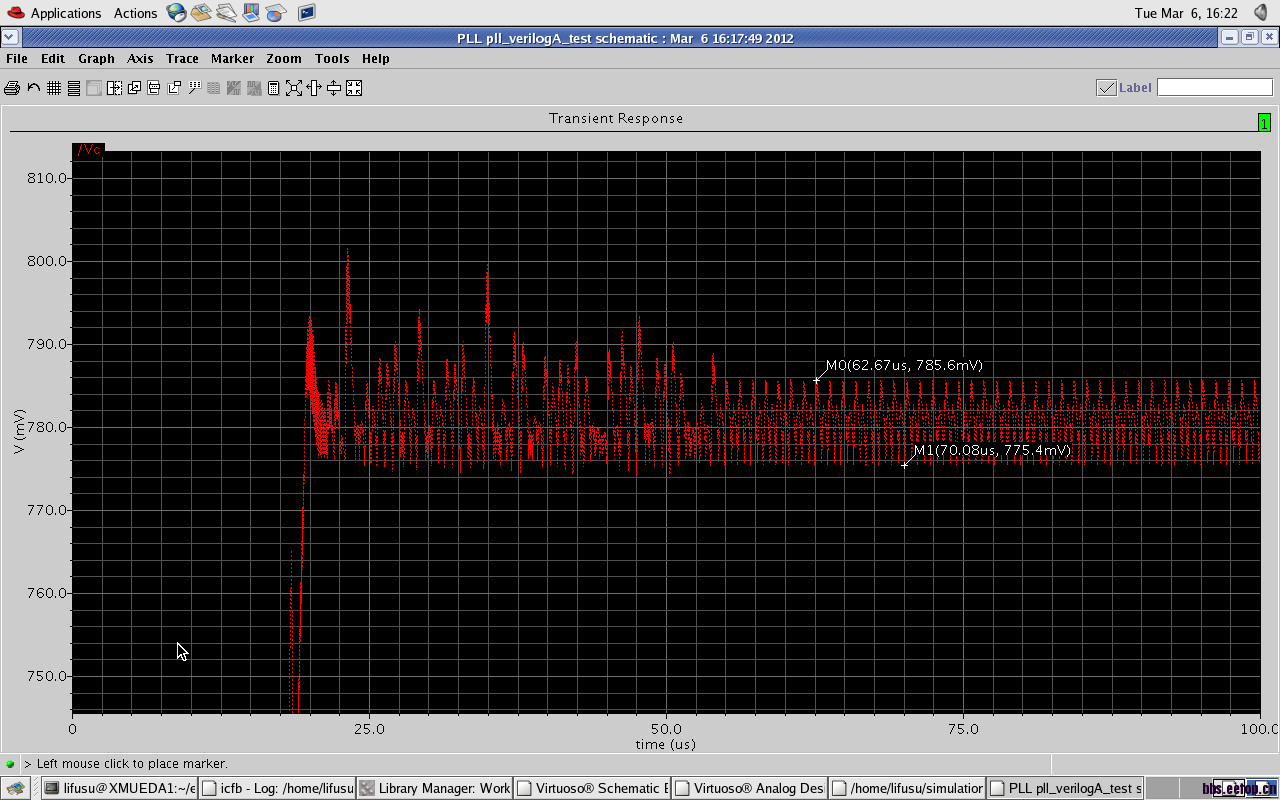

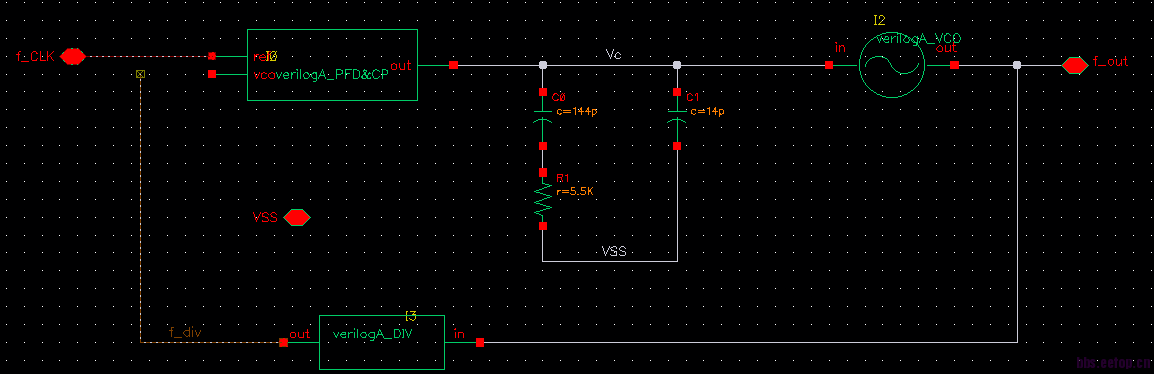

我的pll是用verilogA搭建的,12MHz输入,C2=400p,C1=40p,R2=3.3k,环路带宽=600k,Kvco=600MHz/v,Icp=20uA,锁定时,Vctrl的电压如下,为什么会有这么强烈的杂波、抖动呢?

还有,这种情况只在我把分频器加进去后才会出现,分频器去掉就不会这样了,很奇怪,按道理这个分频器也是理想的,不会影响什么的啊?

还有,这种情况只在我把分频器加进去后才会出现,分频器去掉就不会这样了,很奇怪,按道理这个分频器也是理想的,不会影响什么的啊?

你可以做一个三阶滤波器试试

加了Div之后的环路特性看过没有?

我把tran的精度调成空,也就是什么都不选,这时就不会出现上述现象,原先是选的最左边的精度。

这个按道理应该是精度最高时最准确吧?空的时候精度是怎么样的呢?

这个锁相环的环路特性该怎么仿真呢?我试了把分频器后面的连线断开,然后在输入加一个正弦信号,不能仿真出来。

我先前用的是二阶的传递函数用matlab来作图的。

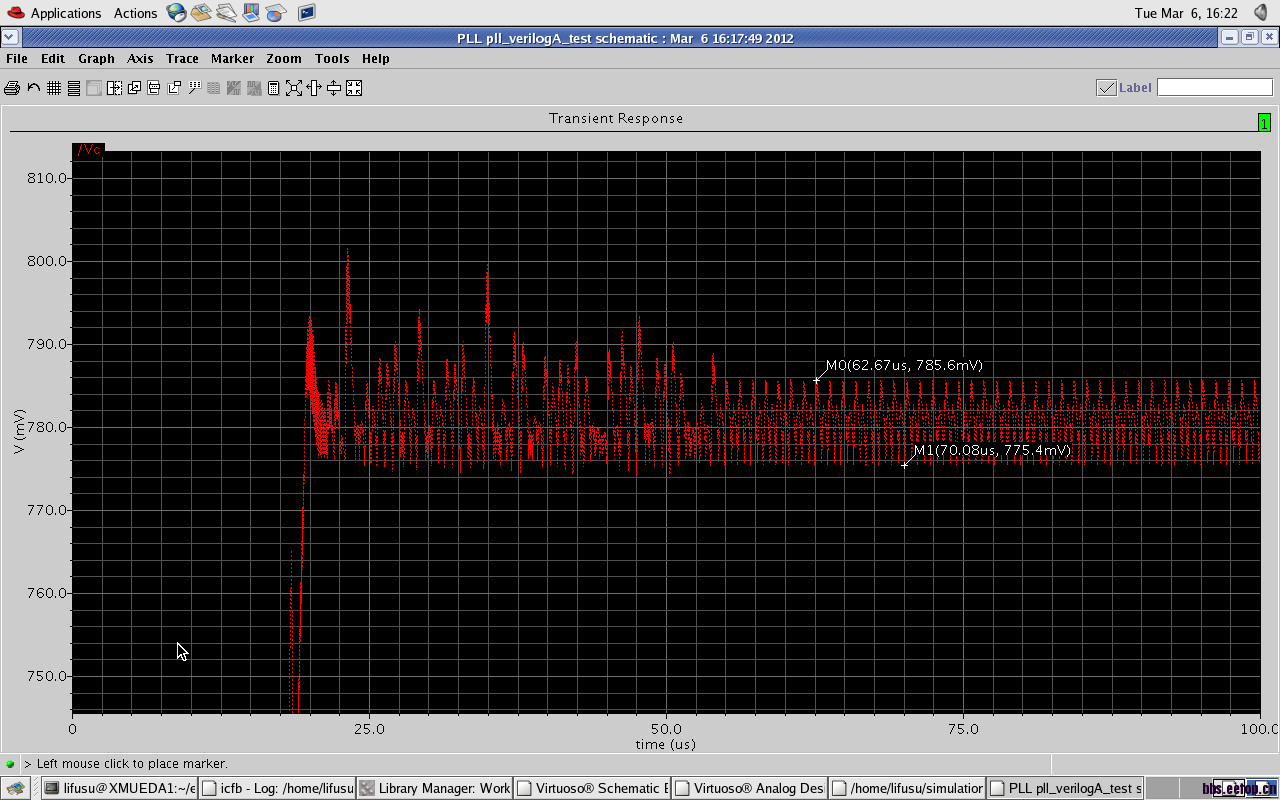

10mV的抖动,大了点,但不能说不正常吧,可能优化下环路参数就好些....

原来的环路分析里面增加一个Divider的Phase Domain小信号模型嘛,然后看看环路特性。

你好,为什么有的分配数不会出现问题,而有的分配数就会有这么大的纹波呢?并且有问题的分配数不是在极端的最大或最小分频时,而是在中间的时候。

那你看一下中间数值的分频时的环路增益和极大极小的差别吧. 你应该知道纹波大小和环路特性的关系吧.

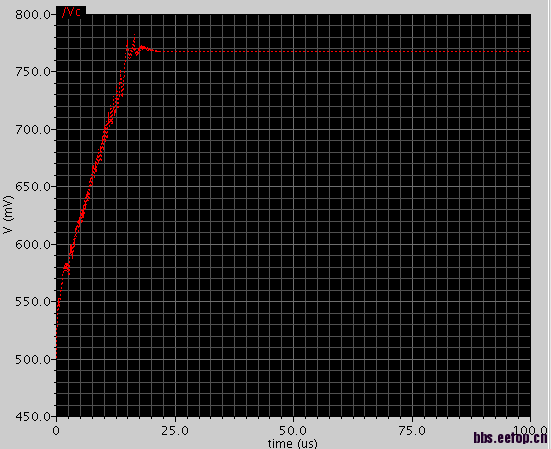

又发现一个很奇怪的问题:

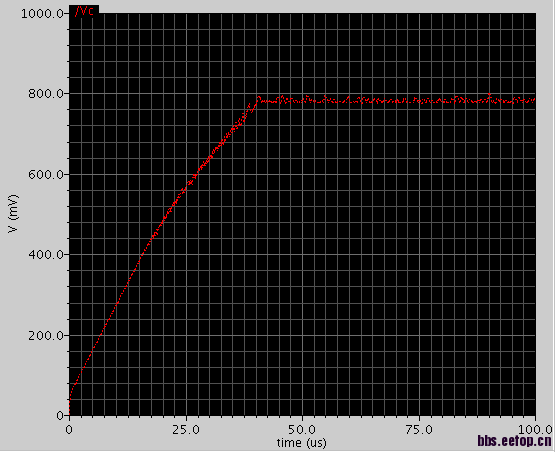

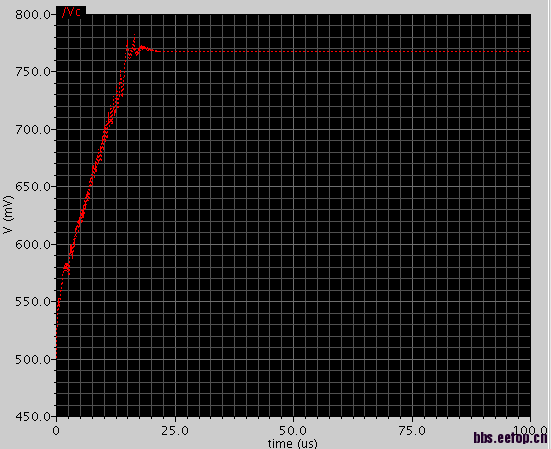

当我将VCO控制电压的初始值设置为0v时,输出抖动剧烈,图一;当我设置为从0.5v开始时,输出完全正常,图二。两个仿真都是verilogA模型,其他条件完全一样。

怎么这么坑爹啊!哪位高手遇到过此问题,救命啊!

hjhgjhgjghjghjgh

你把电荷泵的电流增大到分频比N倍。或者减小LF带宽

我想知道你的带宽是怎样算出来的?还有你的分频比是多少?

学习一下~!

你这个应该是正常现象,没有纯粹理想的一条直线

学习了!

你有看过你输出的FFT吗?

小编解决这个问题了么?

?

最近也遇到这个问题,不过我的环路带宽只有不到100K...