(PLL)D触发器做的PFD,怎么下降沿也触发了?

时间:10-02

整理:3721RD

点击:

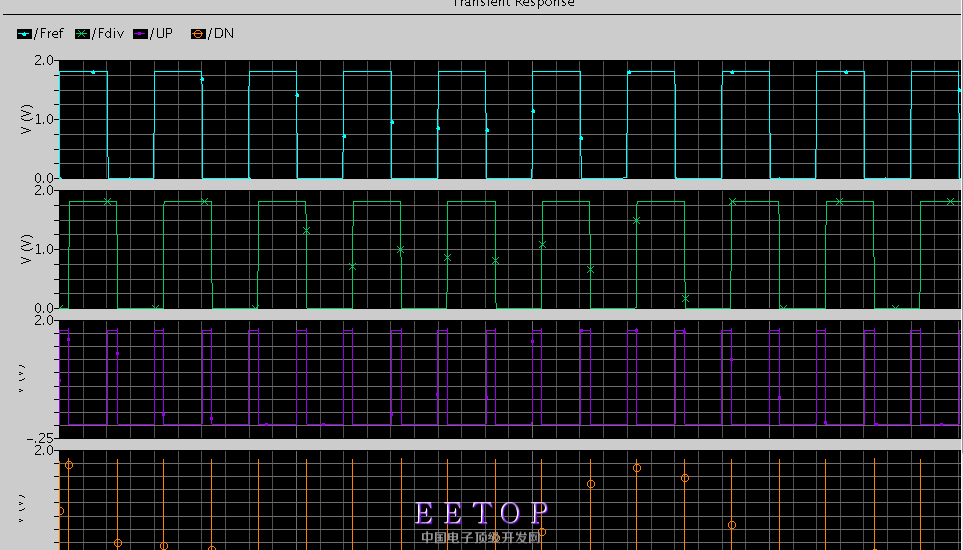

我用razavi书上的图示做了一个简单的D触发器式的PFD,按正常来说应该只在上升沿时触发,但是得到的结果是上升沿下降沿均触发。

想不出来哪里弄错了? 第2个图片显示,第1,2行为Fref ,正常来说1图相位超前2图,仅仅在上升沿时输出他们的差值,可是下降沿时也出现了。

如何调整 使仅仅在上升沿触发。像这个图片一样,明明结构都是一样的啊

你没错。

我是真不太懂,按razavi书上的结果也应该得到仅在上升沿触发(得到像最后一张图片的结果一样),您能详细说说嘛?谢谢

理论分析,应该是只有上升沿触发。

你的仿真结果确实奇怪。

可以把左半边的其它节点波形发出来吗?

是reset延迟引起的, 这个延迟有利于消除死区,一般在设计的时候会额外加延迟元件把这个延迟设计到一个合理值。

你给的激励的上升下降的速率够快吗?一般在1ns之内,太慢的会有问题。