关于全差分运放的建立时间仿真问题

时间:10-02

整理:3721RD

点击:

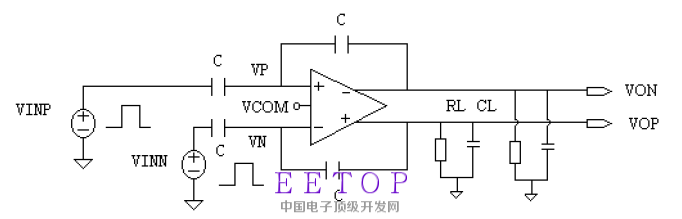

我采用上图所示的仿真电路,为什么当加入不同大小的阶跃信号(比如1mV、10mV、50mV等),测量结果有明显差异?求简答啊,这个问题纠结了好久。

请问怎么加的阶跃信号

给出仿真波形看看吧。

那两个输入信号源用的是vpulse,一个设置是v1为2.5v,v2为2.6,另一个v1是2.6,v2是2.5(单电源运放,确保管子都处于饱和区),当想改变阶跃幅度时,改变v1,v2的差值。请问这样有问题吗?

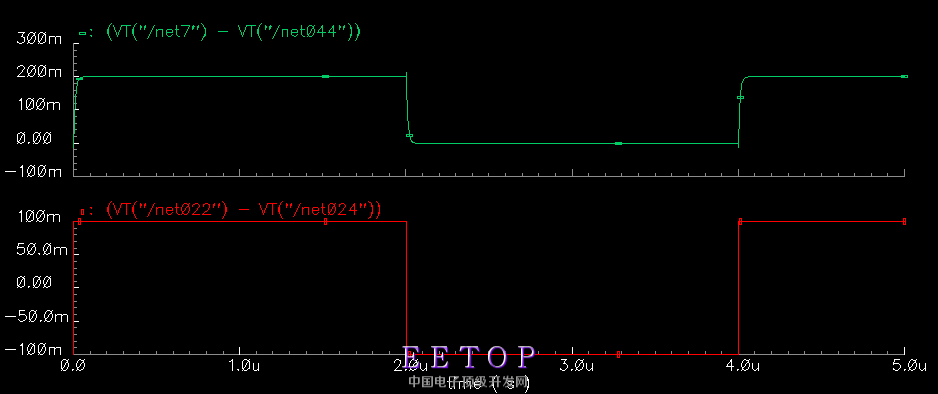

一个是输出差模信号值,一个是两输入信号源的差值请赐教

我想看一下运放正负输入端信号,还有这个运放共模电压和供电电压是多少,使用的是什么结构