动态比较器

时间:10-02

整理:3721RD

点击:

本科毕设要求做动态比较器,题目要求设计一个用于16MSPS Pipelined ADC的动态比较器,要求建立时间小于800ps,比较差值在1mv以下,600mv以上时仍可以得到正确结果。有几个疑问:1、建立时间是不是就是比较器的延迟时间

2、差值小于1mv仍可以得到正确比较结果是不是说失调电压要小于1mv

3、大于600mv要考虑什么情况

恳请大家帮忙解答下,谢谢

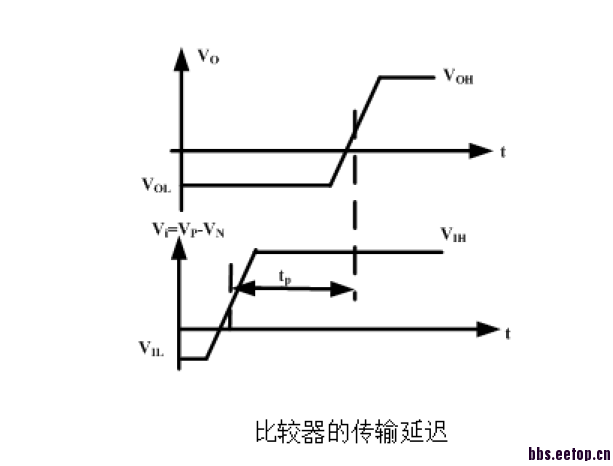

settling time [5]. Propagation delay is the amount of time that it takes for a change in the input signal to produce a change in the output signal [6]. 不明白settling time指的是那段

PS:同道中人啊!

`PMW`X5.png)

2、差值小于1mv仍可以得到正确比较结果是不是说失调电压要小于1mv

3、大于600mv要考虑什么情况

恳请大家帮忙解答下,谢谢

建立时间就是比较器对阶跃信号的响应时间,从阶跃信号输入到比较器输出稳定值的时间长度。

差值小于1mv意思应该是比较器的增益够大,一般比较器由于有限增益导致差值在阈值附近的一段距离内时输出跳变。

600mv可能是要考虑大信号响应吧。

PS:小编你的ID真的很亮!

什么工艺,什么电压,16Mbps的ADC周期是60ns左右,那么半周期也有30ns,你提一个800ps的setting time是不是太不靠谱了, 给个2n-3n又如何,

一般dynamic的比较器很多都是latch 输出,1mv可以得出正确的logic value, 这个没有什么难度。

差值小于1mv得出正确的结果和offset 小于1mv的区别是什么?

settling time [5]. Propagation delay is the amount of time that it takes for a change in the input signal to produce a change in the output signal [6]. 不明白settling time指的是那段

PS:同道中人啊!

`PMW`X5.png)

smic0.18μm工艺,电源电压1.8V 。我也觉得16M的ADC要800ps太过了,但是题目要求的。

这个tp就是传输时延propagation delay ,对比较器来说响应时间和建立时间应该是一个意思吧,传输时延也应该就是响应时间的意思,这个时延和信号的大小也是有关系的,输入信号越大时延越小,但是再大的输入信号还要受到摆率的影响,一家之言啊等着大牛来回复,不过话说经3楼提醒,你的这个要求也太高了吧?

PS:哈哈哈哈

瑪哈嘎拉

小编ID确实亮,2楼也是同道中人啊