高速 Flash ADC 比较器设计问题

时间:10-02

整理:3721RD

点击:

最近在设计一个3bit的Flash ADC,信号频率是2.5GHz,采样率是5GSample/s。但是在做前置放大器和比较器部分的时候就遇到了很多问题,希望做过这部分的大牛能帮帮忙:

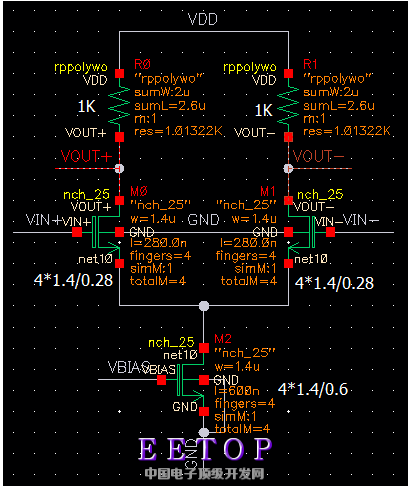

1. 我的Vref取的是1.25V,Vin给的是直流是700mV,振幅是700mV,2.5GHz的正弦信号;Vin和Vref都是单端信号。看很多论文上前置放大器都是用的很简单的结构,所以自己最开始用的是下面的这个:

可是这样的话,和7个基准电压156.25mV,312.5mV,468.75mV,625mV,781.25mV,937.5mV,1.09V对应的前置放大器的输出的直流电位很难控制。

我是应该做一个适合于所有位的前置放大器呢,还是对应于每一个比较的基准电压做7个前置放大器然后分别调整呢。

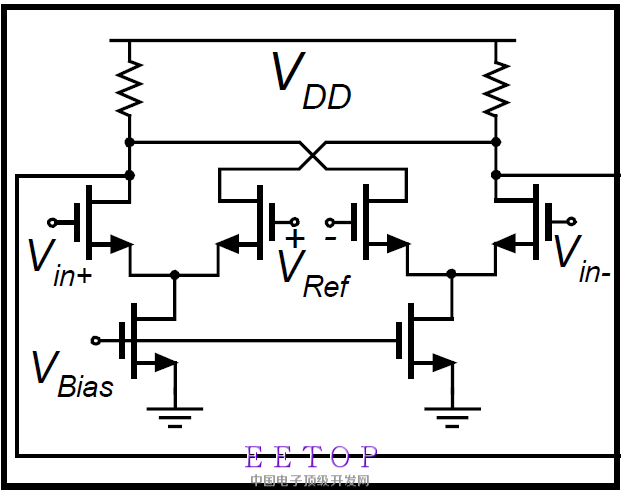

2.还有一点是,看了很多论文里面的前置放大器都是用的差分的结构,不管是Vin还是Vref,如下图:

在这里想问下,差分的和单端的在性能上有什么区别呢。

3.最后想问下,如果我ADC里面不加时钟可以吗,就是比较器做成静态的那种,然后后面再接一个组合电路搭的decoder。因为5GHz的片外时钟可能不太好弄。

现在只是在做前置放大器和比较器部分,但是做得一团糟,也很没头绪。还望做过相关的大牛们能不吝赐教!跪谢!

1. 我的Vref取的是1.25V,Vin给的是直流是700mV,振幅是700mV,2.5GHz的正弦信号;Vin和Vref都是单端信号。看很多论文上前置放大器都是用的很简单的结构,所以自己最开始用的是下面的这个:

可是这样的话,和7个基准电压156.25mV,312.5mV,468.75mV,625mV,781.25mV,937.5mV,1.09V对应的前置放大器的输出的直流电位很难控制。

我是应该做一个适合于所有位的前置放大器呢,还是对应于每一个比较的基准电压做7个前置放大器然后分别调整呢。

2.还有一点是,看了很多论文里面的前置放大器都是用的差分的结构,不管是Vin还是Vref,如下图:

在这里想问下,差分的和单端的在性能上有什么区别呢。

3.最后想问下,如果我ADC里面不加时钟可以吗,就是比较器做成静态的那种,然后后面再接一个组合电路搭的decoder。因为5GHz的片外时钟可能不太好弄。

现在只是在做前置放大器和比较器部分,但是做得一团糟,也很没头绪。还望做过相关的大牛们能不吝赐教!跪谢!

额,上面的“1”里的图没放上去