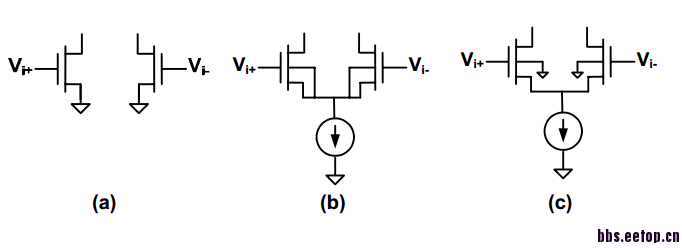

三种差分对(有无尾电流,衬底是否接地)的CMRR比较

比较3种差分对的CMRR

EE240-2010中的L11讲到这个问题,前几天笔试也碰到(选C,估计错了),根据EE240的说法是B好点。

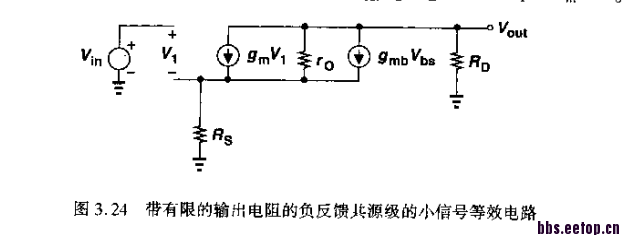

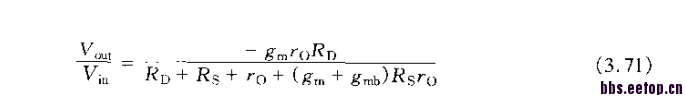

但是从Razavi书中P52-3.55和P56-3.71公式来看,衬偏效应减小了Acm,

如果认为Adm相同,(?考虑衬偏还是虚地么?)

那么根据CMRR=Adm/Acm考虑的话,感觉C的CMRR要好一点。

自己顶一个,求解答

选2的话衬底到地的漏电流如何考虑?

不用soi或者埋层还没人敢这么接。

deep nwell就是埋层

埋层貌似不是这个作用

埋层可以起到隔离的作用

每个工艺都有dnw?工艺中每个管子都能用dnw?

光有个埋层做不到这么接法吧

题目这么出了,不少工艺也是可以这么做的,你为何要纠结每个工艺或每个器件都能这样做呢?

折腾了半天,没人回答小编的问题

还是你懂我

这就是个题,不是工程实际

我现在的问题是根据书上计算是C的CMRR好,可是EE240说B好

晕,EE240和Razavi不是说的一回事么?衬偏效应降低了Acm,所以衬底电位越高CMRR越大啊。

拉神明明说的是有衬偏效应的会降低共模抑制Acm当然是增大了····

选B····

是降低CMRR还是Acm?我读书少,你别骗我。

因为共模增益增大了,所以共模抑制降低了,难道不是这样吗?小弟读书比h博士少很多,诚惶诚恐啊,求指教

和工艺相关,B和C比较是认为C的接法会在差分对的源极引入电容,对高频信号起短路作用,共模增益增加,CMRR减小,准确的讲引入一个极点,CMRR高频时减小。

仅供参考。

"晕,EE240和Razavi不是说的一回事么?衬偏效应降低了Acm,所以衬底电位越高CMRR越大啊。"

是啊,根据书本我也认为是衬偏降低了Acm,进而CMRR更大,可是EE240说B的CMRR更大

” 拉神明明说的是有衬偏效应的会降低共模抑制“

求教,在课本哪说到了?

你打错了吧,没懂你说的逻辑

共模增益怎么就增大了?说详细些嘛

小编说的是降低了Acm,你说的是降低CMRR,这俩正好相反。很多年不看拉神的书了,原话怎么说的?

仔细分析一下,我觉得你可能搞错了。衬偏应该会增加Acm。尾电流正端,也就是mos管s极,是受共模电平控制的,C图中这个节点会通过背栅调制作用影响输出的共模电平,而B图不会。

所以答案确实是b。

而衬偏效应还会导致输出电阻降低。Adm应该也会降低。

呵呵

考虑衬偏效应的小信号模型和增益如下图,gmb出现在分母里,还是减小了Acm啊

这个怎么叫Acm?

共模半边电路不是这样么?

如果这个是Acm,那Adm呢?没有差分对,就没有所谓的共模、差模。

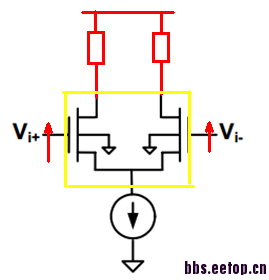

如图考虑差分对

如果尾电流理想,那么黄色内部等效为一个黑盒的话,

由于黑盒两端没有电流的变化,vout的共模不变,这么说是否合理?

如果尾电流阻抗有限,就回到了上面的差模半边等效,这是否合理?