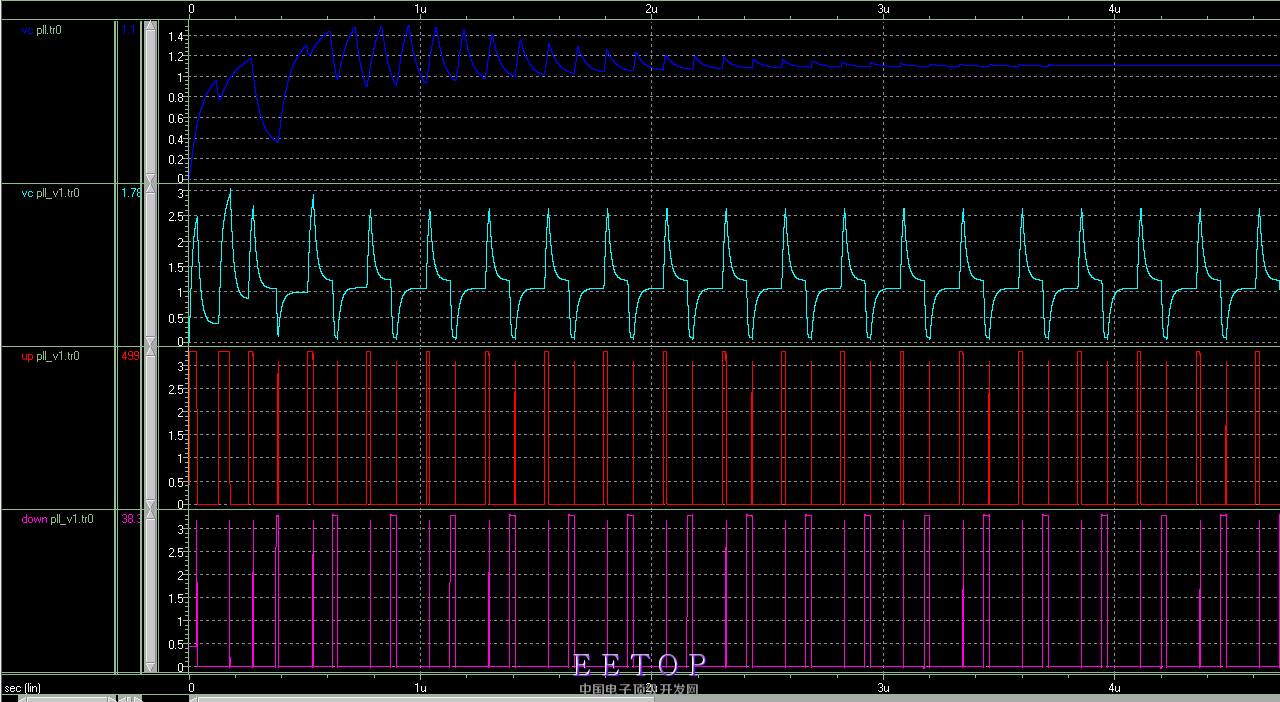

锁相环VCO的控制电压这个波形是什么情况?

没做过CP的PLL,个人感觉是把增益调大了之后导致稳定后的误差很大

最后是锁定了啊!

是锁定了吗?不过我感觉VC变化很剧烈啊,有点怀疑是不是在震荡,凭你的感觉造成这种现象的原因可能是什么呢?

那你是直接用的PD结构的PLL吗?现在CPPLL见得是比较多啊,按照你说的,环路增益大了之后,稳态相位误差比较大,VC波动就比较大是这样吗?可是我这个波动有点大的吓人啊,我都有点怀疑这不是波动而是震荡啊

我这样理解的:

最上的是经过环路滤波的,第二个是PHD 输出的,第三四分别PHD输入的。对不对?第一个图尾部成了直流,这样看来是锁住了( 不管其他性能的话)

不好意思是PFD啊

电路呢?

是Hspice仿的,没有图只有网表,做得不是很好,就不贴上来了,只想问问,改了CP电流和LP的R、C之后,控制电压就从第一个波形变成了第二个波形,第二个波形的VC能否反映环路是否入锁?

第一个波形是LP滤波之后输出的,当然环路最后是入锁了的,第二个波形是修改了环路参数(增大CP电流,改变LP电阻电容)之后LP滤波输出的,第三个和第四个是PFD输出或者说是CP输入信号,我想问的是第二个VC的波形能否反映环路已经入锁?

额,波动差不多都3V了,怎么可能锁定啊。你改变电流和R,C之后,环路相位裕度你有计算过吗,感觉你这环路不稳定啊

计算一下bw吧

bw太大了

额,带宽大了之后为什么会这样呢?

算了下没有改变参数之前,带宽是1MHz,改变参数之后带宽是3.5MHz,参考频率都是7.8MHz

没改参数之前PM=65度,该参数之后PM=48度,感觉不是环路不稳定,而是稳态相位误差太大

带宽太大了,理论上环路带宽不能超过参考频率的1/10,实际中经常在1/20以下,你取了这么大的带宽目的是啥呢

目的是想快速入锁,入锁后再想办法将带宽降下来

带宽一般要低于fref*1/2pi,从而可以用小信号模型去近似。过高的带宽lpf无法去掉杂散,所以vtune上的周期抖动很大

嗯,多谢指点,你说的带宽太大lpf无法滤掉参考杂散我觉得很有道理,vtune上面的变化与fref是同步的。带宽是应该小于fref/20,以满足小信号线性近似的吧,你确认下你是不是打错了呀

第一个VC的波形就是带宽小的时候的情形啊,是能锁定的,感觉19楼说的有道理,带宽大了参考杂散大,而不是不稳定。另外带宽和环路稳定与否没有必然的联系吧