Ring VCO 相位噪聲測試值較大

VCO_simulation:

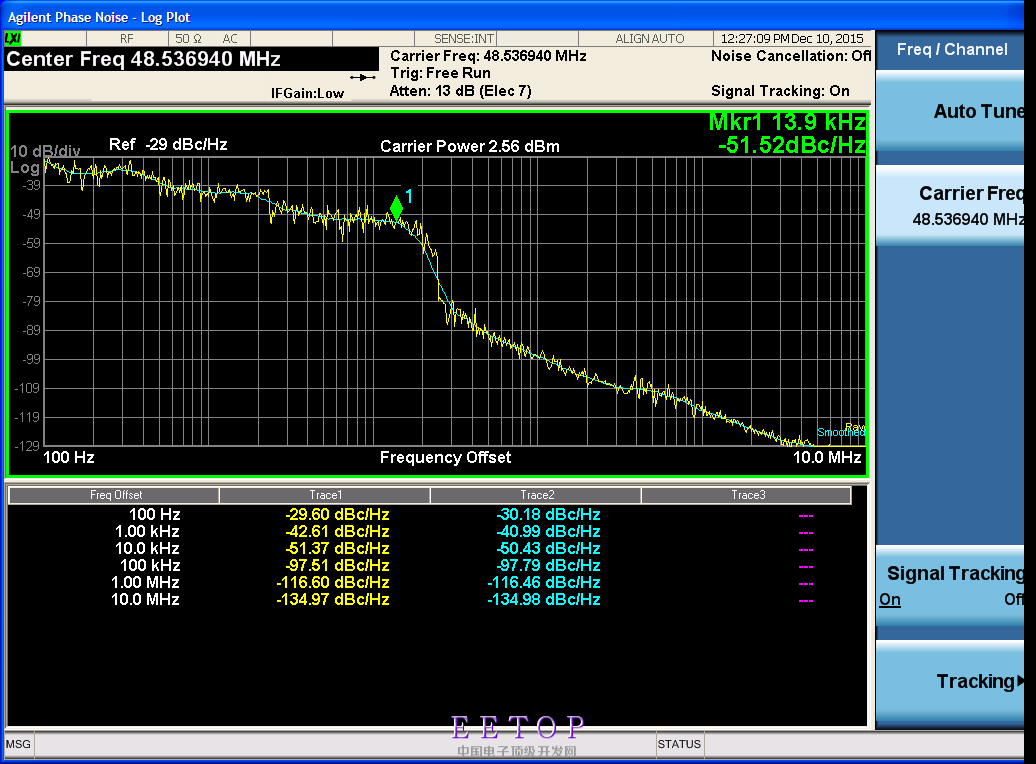

Openloop_meas:

感觉你这个带宽不是3k啊,像是10k多一点。其实我也是新手,说的不对望指正。

Device's Flicker noise

Open measure圖片是開環測試VCO Phase noise的圖

There are some fliker noise parameter in model. I can get 1/f^3 phase noise curve.

You meas the silicon fliker noise is larger than model?

Open loop 測試數據來看 20Khz之前的phase noise突然增加,并且不符合VCO Phase noise計算值

PLL的开环单位增益带宽不就应该是闭环的-3dB带宽么?另外如何测 VCO的噪声呢?片子测试的时候可以把VCO和前面的电路分开么?

一般工艺厂商提供的flicker noise的model精准度在较低频偏处是有限制的吧 怀疑几KHz及以下时 device model的flicker noise有偏差并且离散度较大并且ring oscillator对flicker noise上变频的抑制本来就很差据cadence FAE讲pss&pnoise仿真时output log中linewidth值以下时的phase noise仿真曲线并不很准确 仅供参考。

多谢分享,正需要

設計PLL時,有寄存器可以設置open loop和close loop,open loop時 VCO 的VCON信號可以從PIN外灌信號。

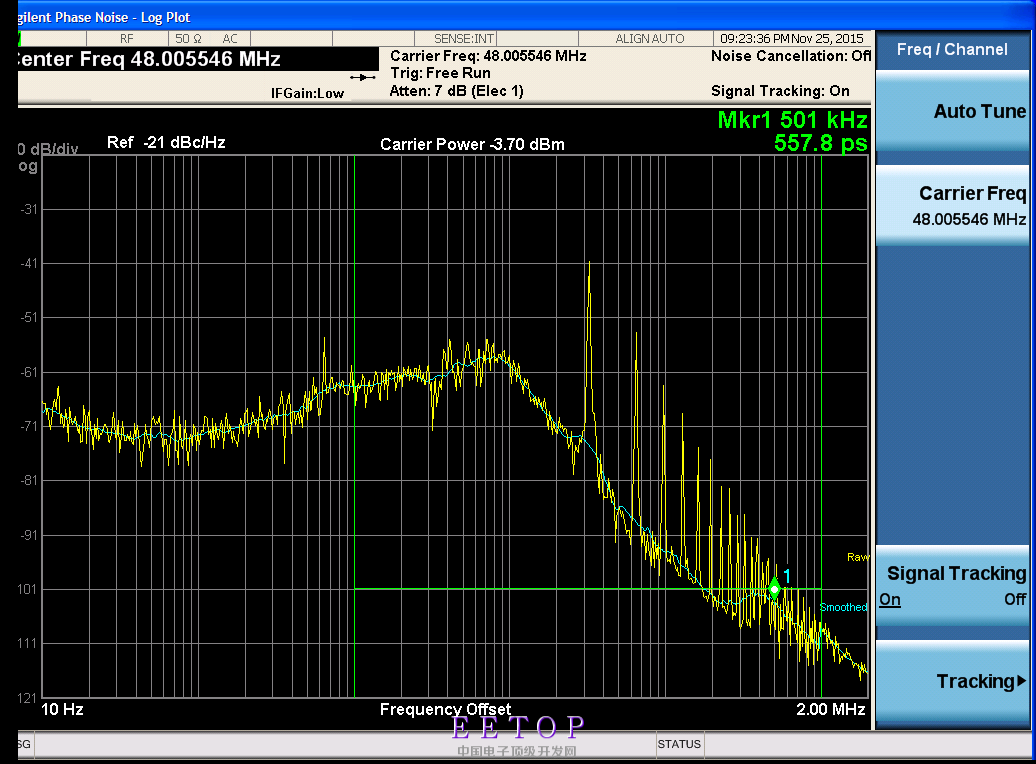

謝謝分享。用EZJIT分析儀測試出來的,Period Jitter比Phase noise積分出來的小很多。EZjit測試出來的PJ=10ps,積分1KHz-1MHz時RMS Jitter=400ps。想討教一下原因。

附上頻譜分析儀測試出來的Phase noise積分波形,1KHz-1MHz 積分后RMS Jitter 550ps。同EZJIT測量結果Period Jitter相差很多。

哦,这样啊,懂了~

不能直接将period jitter与积分出的phase jitter相比,考虑相同的频偏范围period jitter一般比phase jitter小的,因为从phase noise得到period jitter需要在积分项里乘以一个系数sin(pi*f/fs)^2,这个系数在频偏较低时的值也较小,一定范围内相当于“高通”作用,而你这边正是低频偏处噪声较差,自然两者结果相差较多。

谢谢,学习到了

Correct andThanks.

頻譜分析儀積分出來的是RMS Phase jitter. 示波器測試出來的是period jitter. 頻譜分析儀是否可以測試出Period jitter呢?