sc multi-bit delta-sigma调制器reference buffer疑问

时间:10-02

整理:3721RD

点击:

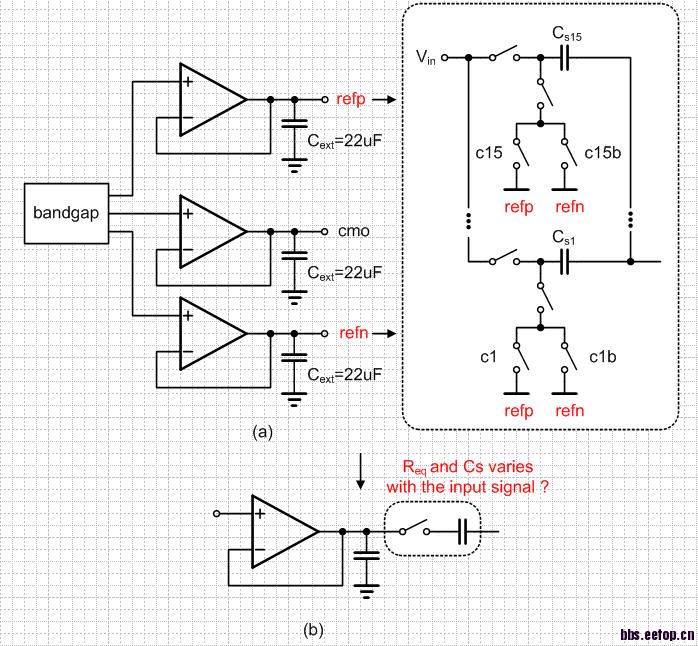

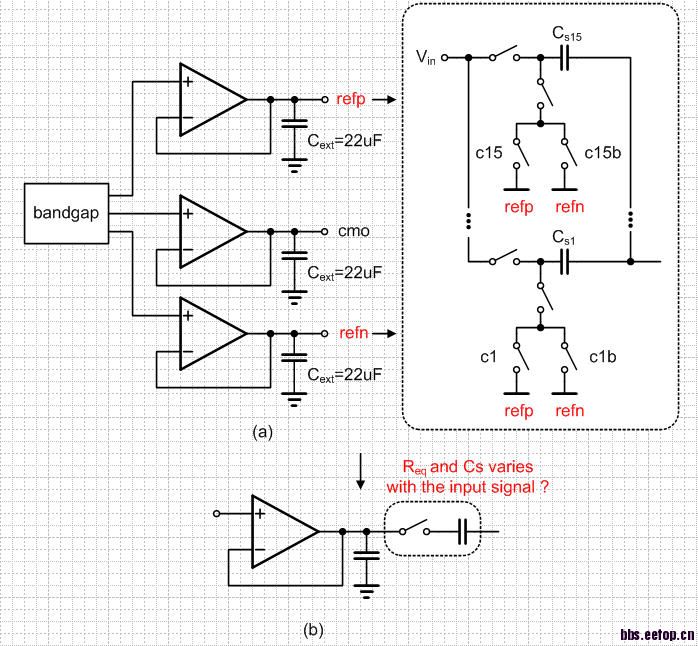

如图所示,调制器采用采样电容与内部DAC电容共用的结构,bandgap产生的参考电压通过buffer外接大电容输入到电路内部,但是buffer接多少开关和电容负载是跟信号幅值相关的,等效模型如(b)图所示,我现在的仿真波形所下图所示:

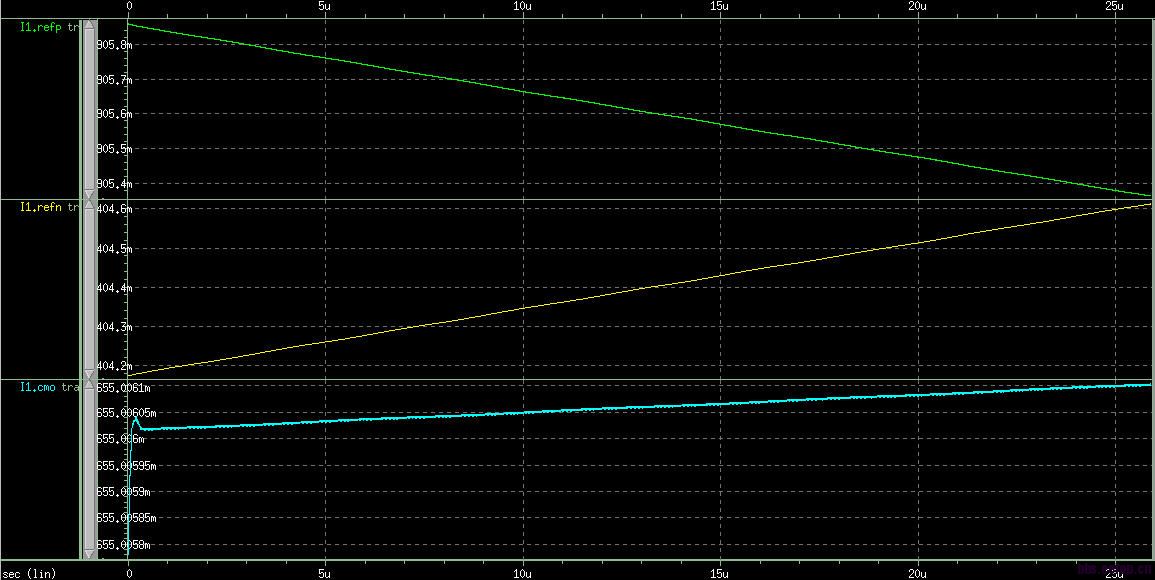

我的采样率是100MHz, 才跑了25us多,refp,refn就已经偏了0.4mV, 我现在的指标要求达到snr 80dB左右,这样大偏差显然是不能忍的,由仿真波形来看,refp,refn根本没有稳定,而cmo信号由于不像refp,refn接了很多负载,所以能很快稳定,但是与信号相关的这种负载的变化怎么能控制,是我的buffer不够强大吗? 请各位大大指教啊

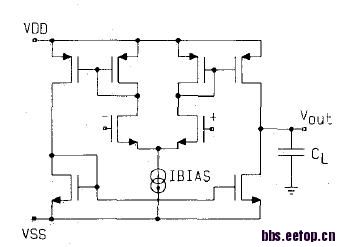

下图是我用的buffer结构,最简单的这种:

自己顶一下,请大家指点一下啊!

BW and Gain is not enough to lock the BGR and output of buffer...

我现在仿真时buffer后面挂了一个大解耦电容,buffer的主极点完全由这个解耦电容来决定,被拉得很低,那么在设计buffer时,在testbench里应该给它挂一个怎样的负载呢,是根据后面电路的实际情况估计一个值吗? 另外,如果要挂大的电容负载,这个buffer的gain和BW一般应设计到多少呢?~

同等答案

顶一下,留意留意,被22u的负载震惊了……

你的buffer的输出驱动电流太小,无法维持片外电容周期性损失掉的电荷量。

建议增大buffer输入级增益,减小静态时输出驱动级的过载电压(增大输出管子)。带宽啥的不用管,保证内部极点不影响稳定性就行