请教一个每级1.5bits的流水线ADC中的开关电容比较器的问题

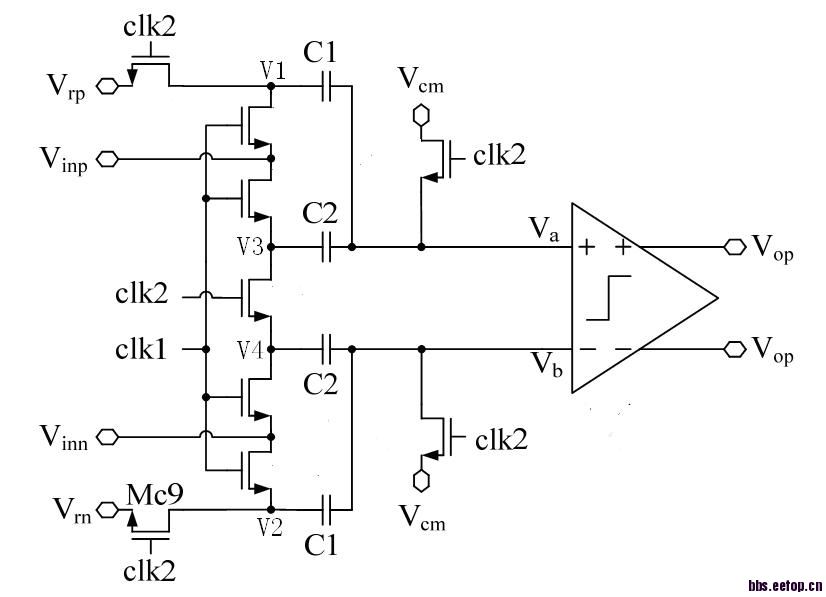

向群里的兄弟请教一个问题,这是每级1.5bits的流水线ADC中的开关电容比较器,有一点我不太明白:

图中Vrp为1.75V,Vrn为1.25V。

图中C1为0.075fF,C2为0.225fF。

有Va-Vb=(Vinp-Vinn)-1/4(Vrp-Vrn),但是通过仿真发现,Va-Vb的值比(Vinp-Vinn)-1/4(Vrp-Vrn)要小。不知道什么原因。

而且通过仿真发现V1~V3是能够等于Vinn和Vinp的,说明里面的开关不是关键问题。

增大C1、C2,会使Va-Vb的值逐渐接近(Vinp-Vinn)-1/4(Vrp-Vrn)。不知道什么原因。

时钟要两相不交叠

我的 时钟的确是不交叠的!

你没有算comparator input capacitor?

C1为0.075fF? 是0.075pF吧,这个值可能太小了,别忘了还有comparator input parasitic cap

C1,C2你是怎么算出来的,这么精确

回复fuyibin 和fuyibin :我的电容的确是0.075pF和0.225pF。但是比较器的输入寄生电容对结果有什么影响呢?

回复ch_00776:这个电容值是我假定的值,因为结果不正确,肯定还是要有改动。其实对电容值的确定,我也没有计算的方法。

还请各位大牛指点一二啊!

比较器我还没有研究。请问你1/4怎么来的

不过采样电容感觉有点小:1.根据ADC的分辨率,最小电容要满足热噪声小于量化噪声

2.是在系统什么位置,是前面还是后面,后面可以较小

3.根据通过系统仿真确定电容值,这个的话看snr的接受范围了

对于10bit的ADC,最小采样电容0.052pF,不考虑其他非理想因素

不足之处,请大牛们指正

这个电容和采样电容没神马关系,是比较器产生1/4 vref的,也可以用flash ADC,不需要太精确。

这个是比较器,和采样精度没关系。电容小点没问题,只要mismatch+offset控制在1/4vref这个范围内,就能被校正回来

谢谢哦,我再看看论文

之前都是用的FLASH ADC,学习下。

顶一个 别沉了

这里电容的大小,最关键的是考虑前面MDAC的负载情况, 1/4是因为两个电容之间的比值为1:3

请问,比较器电容的大小怎么确定呢?

再次重复ch_00776 提出的问题。

关键问题是电容的大小对Va-Vb的值有什么影响?仿真发现,Va-Vb的值比(Vinp-Vinn)-1/4(Vrp-Vrn)要小。不知道什么原因。

不知道说啥好,前面的人已经说得很清楚了,你的c1 c2值太小,和comparator input cap相比可能是一个量级的。自己做个电荷守恒的公式推导就明白了,不思考只会张嘴在这里问,和spice monkey有啥区别?

wocaishidac 同志应该是一个很严厉的人啊。

这个Pipeline ADC是用0.35的工艺做的,采样频率是50MHz。其实以前我也用0.5um的工艺做过,采样频率是10MHz。但是在0.5um工艺下,没有发现这个问题。我感觉0.5um工艺下管子的寄生电容应该更大一下吧。

我采用dj_max 和fuyibin的意见。在仿真时没有把电容和Va直接连在一起,而是通过一个增益为1的VCVS连接,这样电容C1和C2应该不会受到比较器输入寄生电容影响了吧。但是仍然出现Va-Vb的值比(Vinp-Vinn)-1/4(Vrp-Vrn)要小的情况。

另外问一个问题:我的MDAC中的采样采样电容Cs和反馈电容Cf都是1pF,就现在来看,前一级放大器的负载电容是3.6pF。如果增大C1和C2,以便忽略比较器的寄生电容,那么会直接导致前一级放大器的负载电容增大啊,能达到5pF吧,有点恐怖啊!

恳请各位大牛指点一下,谢谢!。

我觉得这个问题并不难debug

va-vb比理论值小多少?

误差源总共有三个:一个是和vcm相连的switch charge injection,一个是comparator kick-back noise,最后就是comparator input cap,逐个检查,逐个优化问题应该能解决

另外运放负载3.6pF是怎么算出来的?

前一级放大器会接2个开关电容比较器,于是有了0.6pF的电容;前一级放大器还会接下一级的增益级,于是有2pF的电容;最后放大器还会接本级的1pF电容,因此一共有3.6pF的电容。

不解?

你两个电容的输出点电压不同,所以charge injection and clk feedthrough是不一样的

减小共模开关的尺寸试一试

75fF/225fF的电容差不多够了,太大loading太重

请问,运放的负载电容怎么确定,我记得是(3/2)Cs,这和小编说得不一样,bin哥怎么看啊?

先理解了反馈系数再算负载电容

回复wocaishidac:我的采样保持电路只有一个Cs,因此反馈系数为1。一共是3.6pF的电容

回复fuyibin和wocaishidac :赞!

这个反馈电路的负载电容算的有问题哦,本级的等效负载电容应为(1-β)*Cf

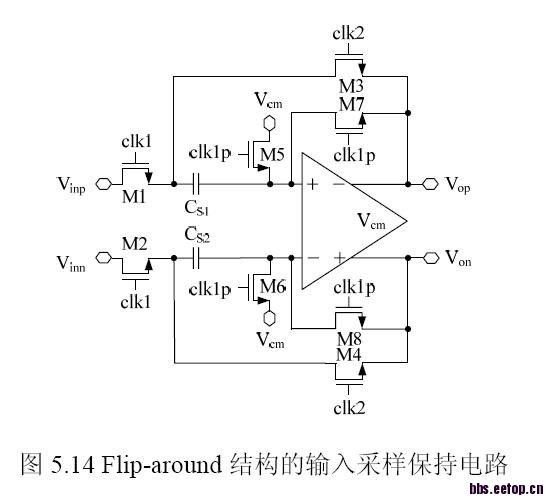

如果采样保持电路如下图:

这个电路的反馈系数是1吗?如果是,那输出端的等效负载电容应不就成了(1-β)*Cf=0了?

所以你没理解反馈系数,flip-around结构可以工作在高频,就是因为反馈系数接近1,导致等效负载很小

同意您的意见!看了我还是嫩了点,继续学习,继续学习!

请教一下,开关的电荷注入效应能通过仿真体现出来吗