cadence仿真不收敛问题

时间:10-02

整理:3721RD

点击:

在cadence电路仿真(用aps仿真的)中,出现了不收敛的问题,具体的如图所示。查看帖子我试了一下把电源电压给一个充电过程,在500ns内从0升到1.2v,但是还是不行,求大神指教。我仿真一个几百ns的会报不收敛的warning,然后还是给仿真完了,但是仿真个几us的就先出现一堆不收敛的warning,然后再出不收敛的error,然后自动把仿真给我停掉了。

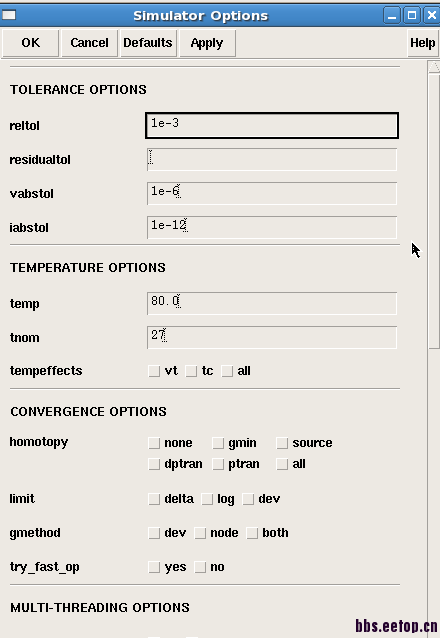

电路图 仿真设置

如果是因为步长导致的不收敛,可以在ADE界面,打开simulation—options—analog,弹出的对话框里有RelTol、AbsTol等值,可以改大些以消除不收敛的问题。但是看你发的图里,应该是电路出现了短路或震荡,在你的仿真步长里电流出现了MA和KA级的跳变或衰减,电压也跳变过大。

仿真设置我传上来了原理图的话是一个adc,特别复杂 贴上来也是一堆的symbol,我就没贴

多谢,设置的精度我贴上来了您帮忙看下,电路有问题我也怀疑了,我再检查一下吧,是个adc,模块还挺多。

修改参数设置试试,可以解决问题的!