DFF sampling window 仿真求助!

我现在就是在spectre里边把clk 和 data由远到近的接近,然后去看clk to Q的delay,但是没有看到由于setup(hold) time violation 引起的超长delay,求教给位是整个testbench不对还是哪里没set好,如果有详细的仿真材料就更感谢了!

谢谢大家!

可以考虑用Hspice的Bisection仿真方法做timing分析, 具体可以参考手册, 以下是目录

Timing Analysis Using Bisection

Describes how to use the bisection function in timing optimization.

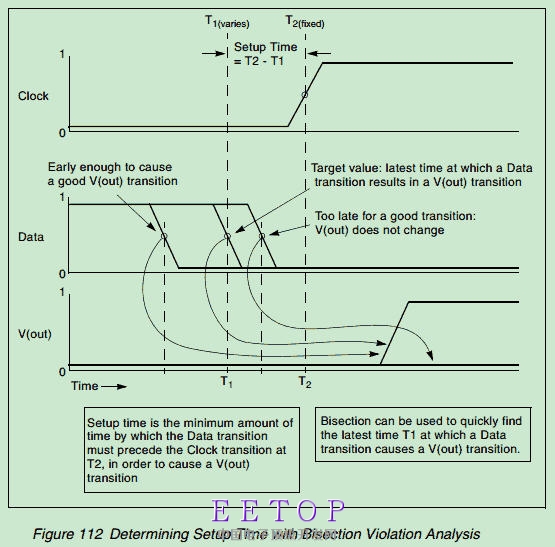

To analyze circuit timing violations, a typical methodology is to generate a set of

operational parameters that produce a failure in the required behavior of the

circuit. When a circuit timing failure occurs, you can identify a timing constraint,

which can lead to a design guideline. You must perform an iterative analysis to

define the violation specification.

Typical types of timing constraint violations include:

■ Data setup time, before the clock

■ Data hold time, after the clock

■ Minimum pulse width required for a signal to propagate to the output

■ Maximum toggle frequency of the component(s)

HSPICE ships numerous examples for your use; see Bisection-Timing Analysis

Examples for paths to demo files.

This chapter discusses the following topics:

■ Overview of Bisection

■ Bisection Methodology

■ Setup Time Analysis

■ Minimum Pulse Width Analysis

■ Pushout Bisection Methodology

■ Using Bisection with Monte Carlo Analysis