關於設計好的OP接成unit gain buffer

时间:10-02

整理:3721RD

点击:

下面是我的hspice

.GLOBAL vdd! gnd!

vdd vdd! 0 dc 1.8

I1 I 0 dc 5u

.SUBCKT OPamp vn vo vp vdd! gnd! net10

MMP8 net10 net10 vdd! vdd! pch W=1.5u L=1u

MMP5 net23 net10 vdd! vdd! pch W=1.5u L=1u

MMp7 vo net10 vdd! vdd! pch W=1.5u L=1u

MMP1 net30 vp net23 net23 pch W=2u L=1u M=1

MMP2 net32 vn net23 net23 pch W=2u L=1u M=1

MMN3 net30 net30 gnd! gnd! nch W=1u L=1u

MMN4 net32 net30 gnd! gnd! nch W=1u L=1u

MMN6 vo net32 gnd! gnd! nch W=2u L=1u

.ENDS

xop vn vo vp vdd! gnd I OPamp

v1 vp 0 dc 0.75

v2 vn 0 dc 0.75

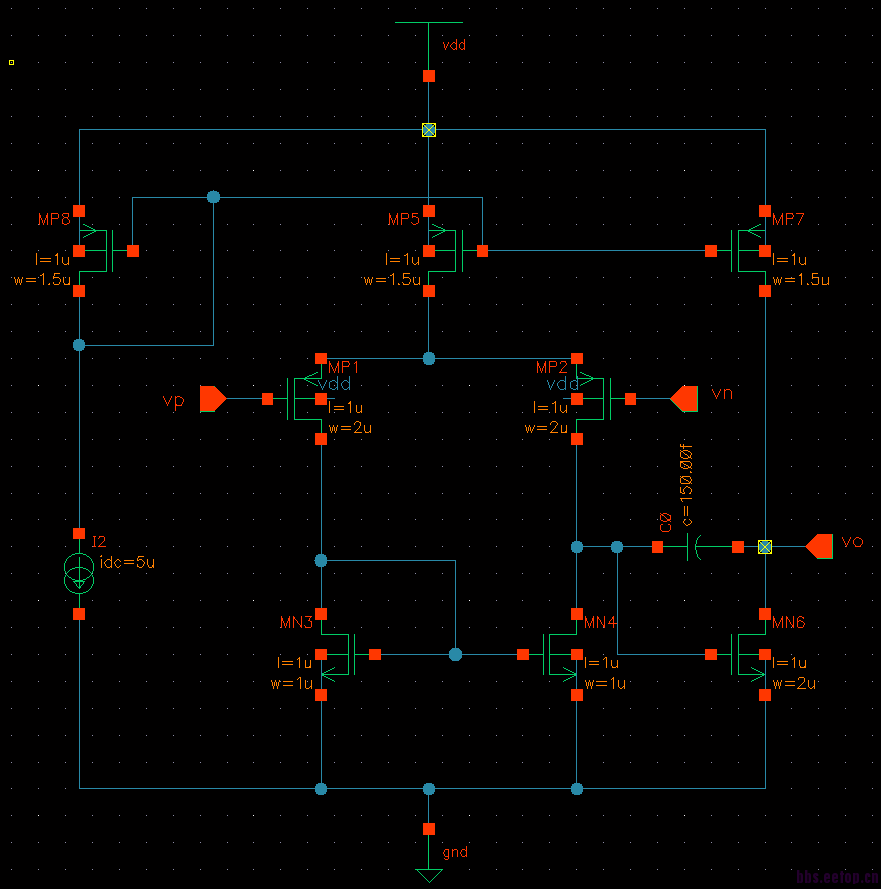

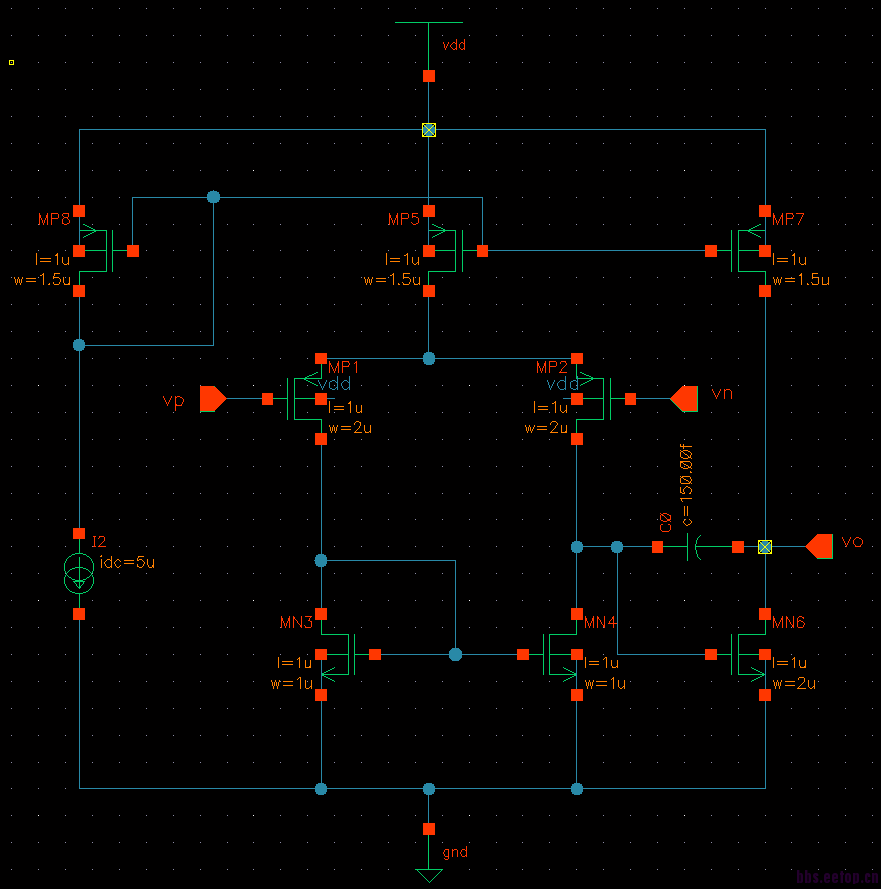

附上電路圖

我設計完的two stage OP

gain=8.3041E+01at=1.0000E+01

from=1.0000E+01to=2.5119E+08

gain_bandwidth=2.3683E+07

phase_margine=6.7499E+01

但是為什麼我一接成 Unit Gain Buffer MN6跟MP2就會進入Thiode 呢?

另外我去掃ICMR不管掃多少就是不能讓全部進到sat...

求大神解答一下阿

另外想問DC點怎麼鎖?如果我想讓輸出擺幅 0.3v~1.5v

那輸出點應該所在幾伏...

還有就是說像這種一端接VDD 一端接GND輸入不是要外加VCM

那這樣設計成一端接VDD/2 一端接-VDD/2不是就可以不用加VCM嗎

麻煩各位了謝謝

因為實際去找0db 頻寬只有97k,但這是不合理阿?增益頻寬應該要固定才對

另外就是一開始問的一些問題能順便求解一下嗎?

謝謝><

.GLOBAL vdd! gnd!

vdd vdd! 0 dc 1.8

I1 I 0 dc 5u

.SUBCKT OPamp vn vo vp vdd! gnd! net10

MMP8 net10 net10 vdd! vdd! pch W=1.5u L=1u

MMP5 net23 net10 vdd! vdd! pch W=1.5u L=1u

MMp7 vo net10 vdd! vdd! pch W=1.5u L=1u

MMP1 net30 vp net23 net23 pch W=2u L=1u M=1

MMP2 net32 vn net23 net23 pch W=2u L=1u M=1

MMN3 net30 net30 gnd! gnd! nch W=1u L=1u

MMN4 net32 net30 gnd! gnd! nch W=1u L=1u

MMN6 vo net32 gnd! gnd! nch W=2u L=1u

.ENDS

xop vn vo vp vdd! gnd I OPamp

v1 vp 0 dc 0.75

v2 vn 0 dc 0.75

附上電路圖

我設計完的two stage OP

gain=8.3041E+01at=1.0000E+01

from=1.0000E+01to=2.5119E+08

gain_bandwidth=2.3683E+07

phase_margine=6.7499E+01

但是為什麼我一接成 Unit Gain Buffer MN6跟MP2就會進入Thiode 呢?

另外我去掃ICMR不管掃多少就是不能讓全部進到sat...

求大神解答一下阿

另外想問DC點怎麼鎖?如果我想讓輸出擺幅 0.3v~1.5v

那輸出點應該所在幾伏...

還有就是說像這種一端接VDD 一端接GND輸入不是要外加VCM

那這樣設計成一端接VDD/2 一端接-VDD/2不是就可以不用加VCM嗎

麻煩各位了謝謝

沒人說明一下嗎

输入的正负标反了吧

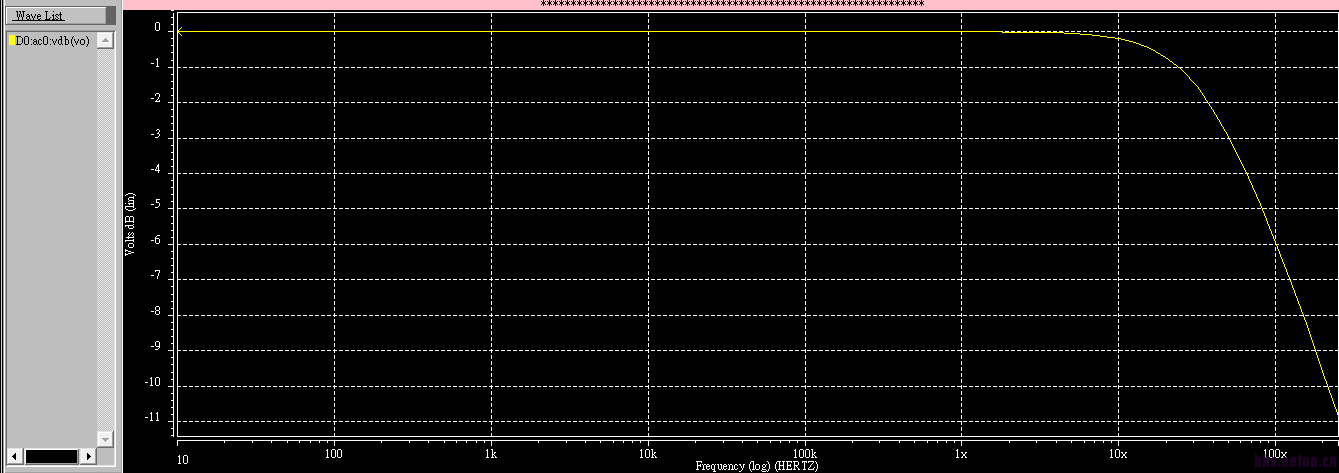

謝謝!換過來之後正常了,但是有個問題是這時候增益頻寬該看哪裡?

因為實際去找0db 頻寬只有97k,但這是不合理阿?增益頻寬應該要固定才對

另外就是一開始問的一些問題能順便求解一下嗎?

謝謝><

看这个

http://bbs.eetop.cn/thread-580714-1-5.html

现在接成了单位增益....此时的-3dB带宽约等于你的开环GBW

你用一个简单的单极点模型就可以推出来了,小编要回去多看看书