关于SD-ADC中的运放

敢问小编用的什么结构?能把大体的系统参数说一下么

我觉得可能原因有下面几个,

1.运放输出摆幅,如果你的输入信号比较大,运放接近满摆幅的时候会引入失真。

2.SR 。这和你用什么形式的反馈DAC也有一定关系。

希望对你有帮助!

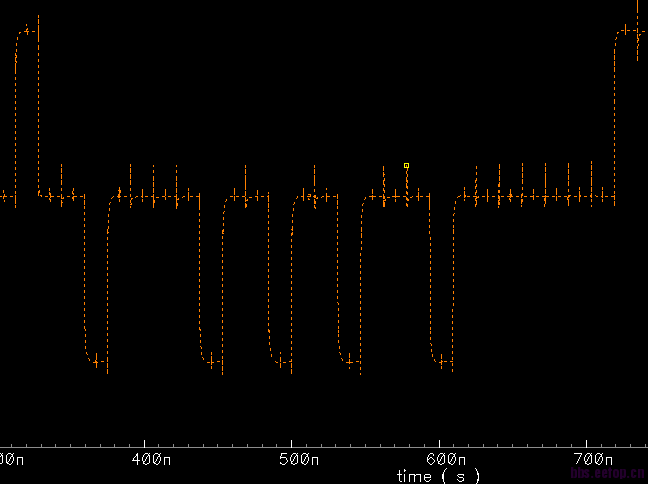

用的结构是3阶8level的连续时间,其中采用了求和模块提前,并且给了比较器半个周期的比较时间,共有三个反馈DAC。Fs为64M,OSR=32。现在第一级和第三级运放的GBW为350M左右,个人感觉已经足够高,继续提高GBW对SNDR没有帮助。我在matlab仿真系统模型时,没有考虑SR的因素,但是我把运放电流加大到接近2mA,SNDR也没有改观,应该不是SR太小造成的。此外,每一级运放的输出我也看了,并没有超出范围。我现在发现的问题是,用理想运放和实际运放条件下,反馈DAC的反馈电流有差别,实际运放条件下,反馈电流的尖峰更大,上升时间也更长,我附上了反馈电流图片。

反馈DAC影响的?

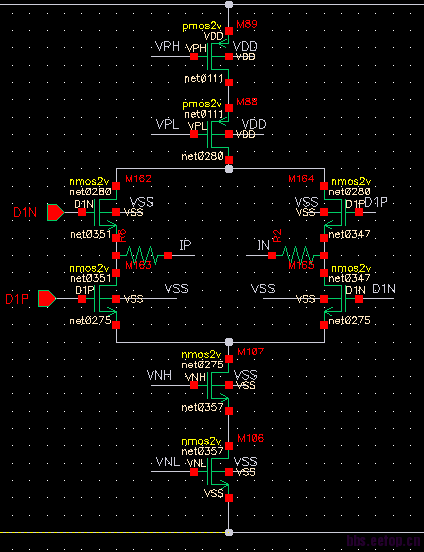

理想运放和实际运放的时候DAC是否都是实际电路?DAC你用的什么结构?

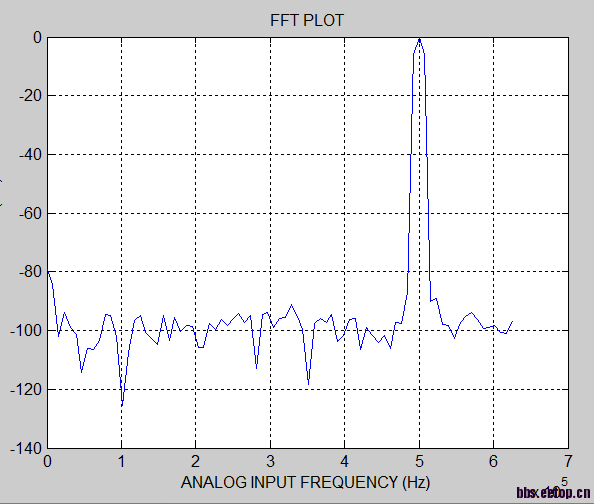

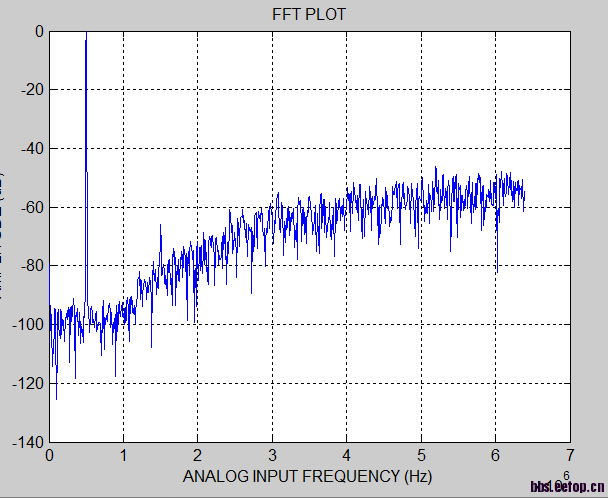

你最好把频谱发出来看看是谐波高了还是底噪高了,看看带外形状怎样才好判断,另外由于实际电路的环路延时,你半周期反馈和整周期的时序关系要调整的。

用理想运放和实际运放仿真的时候,modulator其他部分都是都是实际电路。DAC用的是反馈电流形式,电路图附在图片里,图中的电阻是0欧姆,为了看反馈电流大小的。D1N和D1P的摆幅是1.3到1.8,为了减小电流尖峰

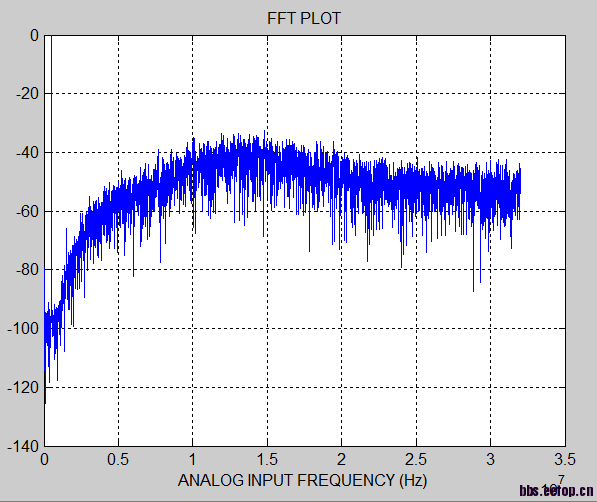

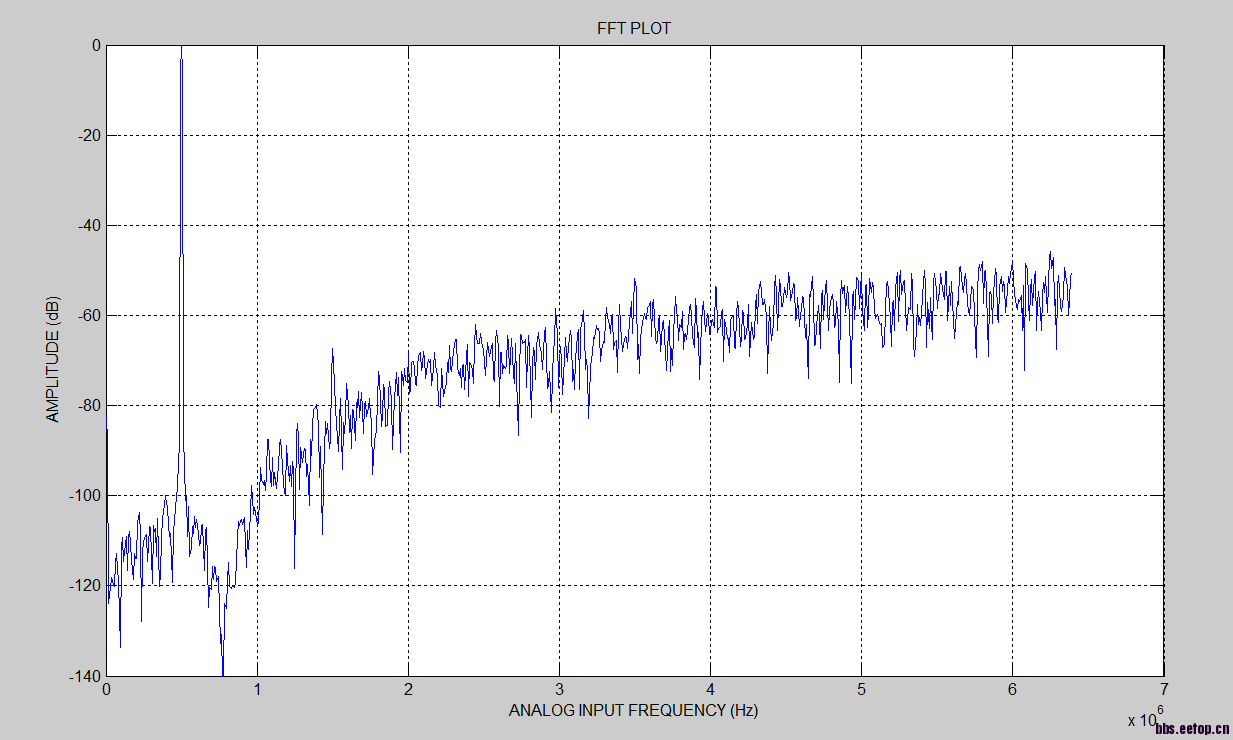

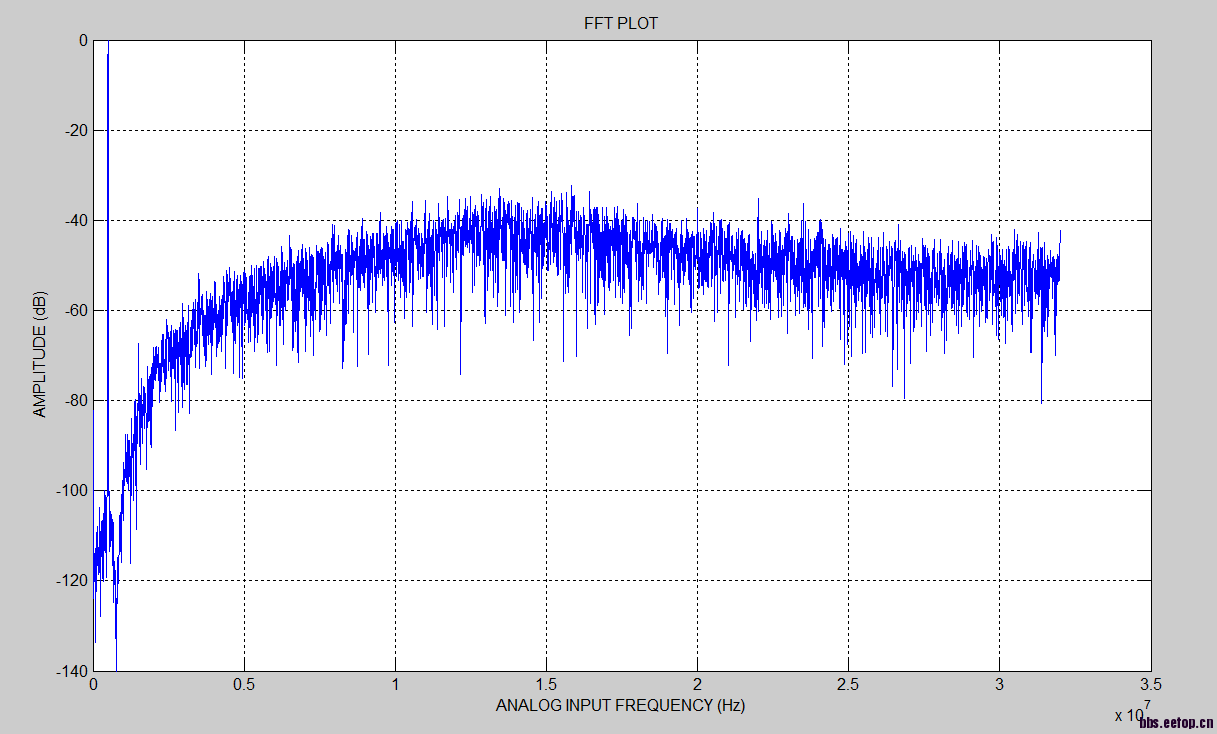

频谱我补充上来了,是底噪高了,应该还是反馈DAC那里出了问题,反馈电流的图片我在上面给出来了。但是不清楚为什么用理想运放的时候,反馈DAC就没有问题,SNDR可以到82dB。另外你说的半周期的时序问题,我没有理解,想请教下究竟应该调整什么电路?

首先检查你的仿真精度设置

是不是由运放本身引入了较大的噪声引起的?

是不是实际运放输入端的寄生电容引起的?

考虑到实际运放的时候电流尖峰变大,我觉得你看看这两个方面会不会有影响:

一个是运放的输入寄生电容,两外一个是你的共模反馈。

输入端寄生电容我之前考虑了,在理想运放输入端接上同样大小的电容,没有对仿真的SNDR产生影响。我不是很清楚你说的共模反馈,不知道要注意哪些方面,是把共模环路GBW做得高点还是别的方面呢?

输入端寄生电容我之前考虑了,在理想运放输入端接上同样大小的电容,没有对仿真的SNDR产生影响。

连续时间SDM里面运放共模反馈不需要做到很高,我的意思是你看看你的共模反馈是否在正常工作范围内

因为如果你是理想运放,环路是没有延时的,那么你反馈的时间点和你建模的设计应该差不多,但如果是实际运放,环路会有延迟,那么你反馈的时间点其实和你预想的已经不一样了,这样每个节点的系数就变了,当然就有问题。看你带外翘起来了,应该就是环路延迟较多的表现,加个理想delay让你量化器时钟延后或者让正周期和半周期反馈提前一点应该就会好。然后再检查你理想运放和实际运放增益是否一致。没仿trannoise的话不用考虑噪声。

我把积分器单独仿真了一下,发现实际积分器的输出不比理想积分器的输出有延时啊。另外我把运放为理想情况的频谱也发了一下,带外的噪声也有点高。但是在带内有零点,这是积分器里的反馈电阻实现的,但是对比一下实际运放的频谱,发现这个零点没有了。应该是系统的系数发生变化了,请问如果不是因为实际积分器的延时,那么还有什么可能造成系统系数的变化呢?

我的运放的共模反馈的工作状态都是正常的

KT咨询专注于ICT高科技行业EETOP官方微博EETOP管理员微博EETOP人人网开源硬件微博

任何不理想因素都会导致系数变化,就针对你这个问题而言,就是理想运放和实际运放的差别,你说你考虑寄生了,而且理想运放的增益我想你也设置的和实际运放相同,那么还有什么原因呢?你说没有延迟,而由于带宽有限,你环路的稳定要花时间,你dac反馈的电流的变化就是因为运放输入端电压稳定需要时间造成电流被调制,在应该的时间点它还没到你设定的值,这不就延迟了吗?然后你后面的积分时间不变,而电流变了,那么系数不就不对了吗?你先按我的方法试试,或者提高你dac输出阻抗

正解,设为consevative 试试

我把量化器的时钟delay了0.2n (Ts=15.625n),得到的结果基本没有变化,难道是delay的时间不太对吗?还有一点就是,既然环路延时了,那么我dac的反馈点也应该延时,好与环路同步。按我的理解,这样就应该是提前量化器时钟或者delay反馈dac的时钟啊,而不是delay量化器时钟或者提前dac时钟

我理解是这样,数据从积分器进来到出去花的时间长了,那量化器不就应该delay一下等等它么?delay量化器,而dac的时钟不变,那么不就相当于dac提前了一点反馈。尤其是你整周期的反馈,你反馈的点的信号可没有延迟,它就是要求你这个时间反馈,如果你延迟dac的反馈不就更错了?你想你做半周期反馈不就为了补偿delay么,所以整体思路还是要提前。不知道你是不是这么做的?可不要量化器和dac一起delay或者提前,那样对于系统来说是没有变化的。还有,只要不超过半周期,调整再狠一点。或者再调整一下你第三极运放的零点,加快环路。

非常感谢,我把量化器时钟延时0.9n之后SNR果然提高了4dB,估计加大延时的话效果会更好。

不谢,加到带外平坦即可

积分器延迟主要是rc决定的,运放引入的额外延迟比较小。还是dac的response在实际运放下被deay了,以至进入下一个周期,仿真中qantizer clock加delay只是又把整个dac feedback waveform搬回到同一个周期内。但是电路实现不现实。可以考虑用rz,delay dac by 1/4个周期之类的,前提clock pn还能满足要求

你好,想请教一个问题。就是我带宽是1M,之前没有考虑谐波,输入信号是500K,SNDR=82dB。现在考虑谐波,输入信号为250K,SNDR=73dB。它的三阶谐波大约为-65dB,请问怎么改善三阶的谐波问题?加大运放增益?另外的问题就是transient noise我之前没有点,现在如果把transient noise点上去的话,下面的空应该怎么设置?

加大增益代价比较大,整个AD就是个单位增益反馈,如果你环路增益大了,稳定性肯定好不了,为保持带宽,只能加功耗。一般DEM一开基本没有谐波了啊,不知你这个谐波怎么来的,DEM用的什么算法?DAC的匹配先做好,然后做开DEM的MC仿真,如果还有谐波再说。trannoise我觉得没什么意义,很慢的,不如你把DAC输出噪声,运放输入噪声仿出来基本就能算出来了。非要仿,fmax选信号带宽2倍,fmin是采样钟/2exp(n),不过以前有人告诉我fmax应该选采样钟频率,所以你还是自己看看help,我当时看了觉得有歧义。

我的DEM用的是DWA算法。DAC不应该有mismatch,我这是前仿,没有仿蒙特卡罗,而且DAC的尺寸取得较大,DAC应该是没有mismatch的。 我现在的问题也是不太清楚较高的三阶谐波是哪里产生的。另外问下什么叫DEM的MC仿真?MC仿真是什么?