cmos器件的一些电容常识

能不能问的具体些?

什么样的cmos器件?digital,analog,RF?

什么样的引脚?电源?模拟/数字输入?模拟/数字输出?单端/LVDS?

您好,抱歉,刚刚才看到回复,这是老师课堂上布置的一个“经验性”问题,他就指点明了两个大方向,一个是cmos器件自身与地的电容通常是什么数量级的,第二个就是cmos芯片工作时它的引脚驱动下一个芯片的电容是什么数量级的(也就是芯片与芯片之间),然后应该是指模拟方面的吧,求解答

这么泛泛的问问题。

不同种类的引脚的电容差别十万八千里。

像一般FPGA的输入引脚一般是10pF左右,模拟芯片的数字引脚也大概是这个量级

而模拟芯片本身不同的引脚就差别很大,而且取决于应用,速度上的要求,高速的输入可能只有1pF,甚至更低

而像Vref这种引脚又有可能达到比如50pF这样,因为会有片上的decap

然而射频芯片的引脚那有效电容就更小了,之所以说有效电容是因为实际的电容可能还是有几百个fF这样,但内部会加电感去中和他,这样输入的等效电容可能只有十几个fF

cmos器件和地之间的电容是fF数量级的,取决于管子大小,一般模拟引脚的电容大概几pF的样子,功率不大的话一般不会大于5pF~

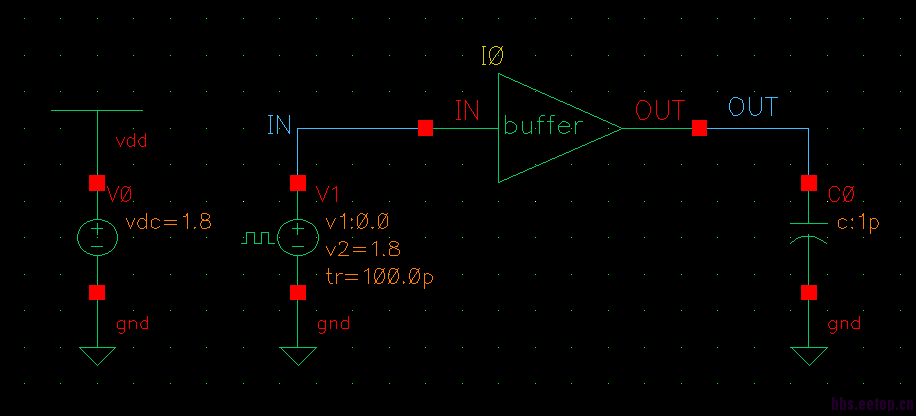

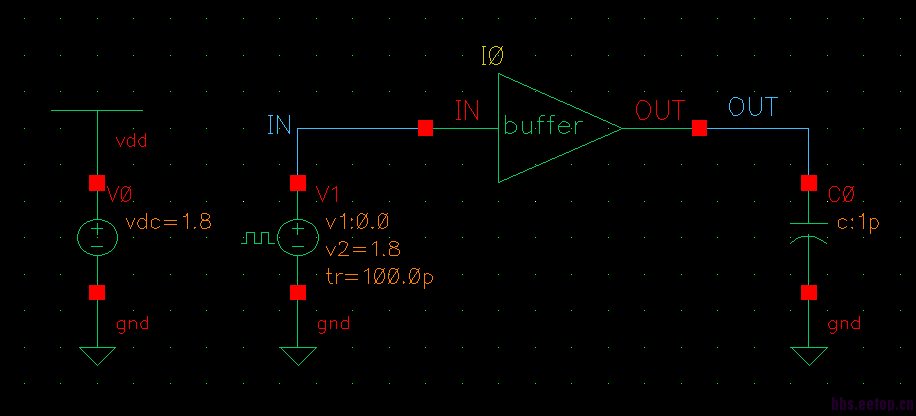

恩,谢谢,我仿了一个缓冲器,它最后面输出级和地之间连的电容设置的是pF的时候,输出就严重失真了,后来设置为变量扫描了一下,发现几十fF的电容就好多了,这个电容应该算是芯片引脚的电容,还是自己内部与地之间的电容啊

恩,谢谢指导了,大神请问

这种电路画在这里一般指的是其输出本身与地之间接的电容,并不是引脚电容~

恩,我仿的时候也是fF级的才不会失真跟你说的很吻合

看起来是数字信号的驱动,这说明你buffer做小了,如果一个数字驱动连1pF都驱动不了,那你白做了。

另外,芯片间还有PCB的传输线,

你去找找FPGA的data sheet,输入引脚基本都是10pF,这还不包括package引入的寄生

这么问太没范围了!

确实很范范的问题,所以说这是一个比较考验经验的问题,老师就是这么刁钻

原来是这样,懂了一些;谢谢解惑

你的时钟多少?100M以上,设计是就要用心多计算一下 驱动能力了

恩,老师没有详细说,原来还要涉及时钟(见笑了,本人现在对这一方面还欠缺系统,整体的把握),所以问题问的问题比较蛋疼,这不,今天老师课上又抛出了蛋疼的课后思考问题