电容失配与pipeline ADC精度

请问如何利用某工艺给出的电容失配来判断需要多大的电容来满足pipeline ADC精度的要求?有没具体公式?

谢谢!

一般来说,由于电容失配引起的级间传输函数的误差要不小于LSB/2,所以,你可以利用级间传输函数来大概估算所需的电容大小。当然,关于Pipelined adc中电容的选择还需要考虑整体信噪比的影响。在精度大于12位时,一般还需采用calibration的方法来提高精度。

了解了解

谢谢!另外,比如某工艺电容的sigma=0.03%,怎么通过估算知道在不进行calibration的情况下,它能支持到多高精度的ADC设计?

算算看:

1个sigma 0.03%, 三个sigma 0.1%,<==>60dB,所以可以做10bit的ADC,呵呵。

上面的计算是有前提的。电容的mismatch是与面积有关的,多大面积的电容mismatch是0.03%?

所以,要反过来,根据你要设计的精度(当然我们假设12bit以下的pipeline,不用calibration)来选取电容的面积,然后定运放带宽和slew rate,然后选运放结构,然后。然后。

sigma是什么意思,为什么要是三个sigma

本人愚钝,可否仔细解释下“1个sigma 0.03%, 三个sigma 0.1%,<==>60dB,所以可以做10bit的ADC”,

为什么要加到三个sigma?三个sigma0.1%怎样判断需要60dB?是和settling accuracy联系吗?如何联系的呢?

还望不吝赐教!谢谢

sigma就是我们学的高斯分布中的标准方差,3个sigma达到99.7%的良率。

0.1%=0.001, 60dB对应1000,一个LSB相当于0.001。所以电容的误差影响不会超过1LSB(当然实际设计是要有余量的)。就是setting的准确性了。

只是粗略的计算,但可观其大略。

[quote]sigma就是我们学的高斯分布中的标准方差,3个sigma达到99.7%的良率。

0.1%=0.001, 60dB对应1000,一个LSB相当于0.001。所以电容的误差影响不会超过1LSB(当然实际设计是要有余量的)。就是setting的准确性了。

只 ...

goodsilicon 发表于 2010-4-29 17:26

sigma为什么要取3个,不是其它

10bit不需要0.1%,0.5%足够了。0.1%差不多可以做到14bit了。

您好,请问这张图出自哪里啊

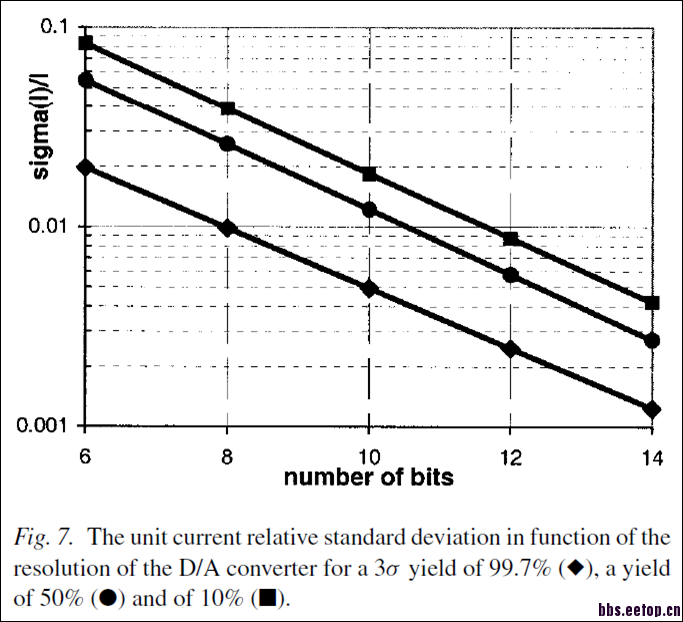

请问,这幅图说的是电容失配对AD精度的影响么,为什么注释是电流标准差?

5楼说的是对的,我说的这个是二进制结构的最小电容(current DAC ,SAR ADC等)。对pipeline line只有两个等值电容不适合。误导你了。

图出自 “An Accurate Statistical Yield Model for CMOS Current-Steering DA Converters”

误差的百分比换算成dB大概就是电容造成的误差能达到的精度,实际还要加上其他的噪声和干扰