动态比较器的设计

时间:10-02

整理:3721RD

点击:

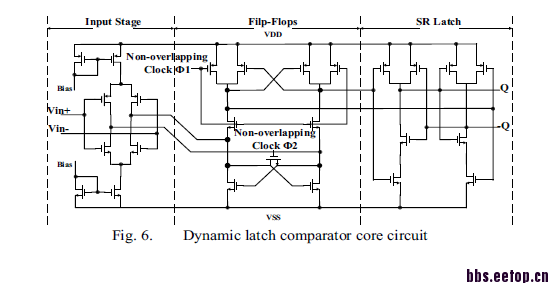

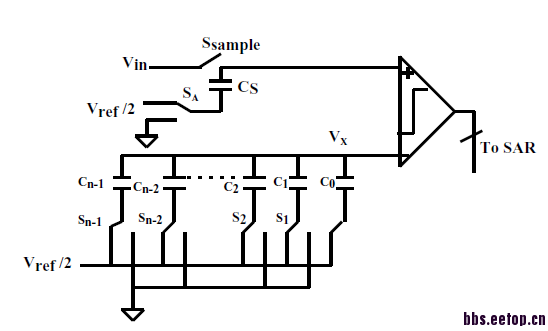

本人新手,最近要做一个12bit的SAR ADC ,当模拟输入电压范围为0-1.16V时,比较器的共模输入范围要为0-1.16V吧,看到比尔做了个12bit SAR ADC时用了上图的比较器,请问那个比较器怎么达到所需共模输入范围啊?还有当clock2变为高电平(复位时),由于时钟馈通效应会使下面两个nmos的栅极电压产生很大的突变,请问如何解决?谢谢!

输入共模不需要信号摆幅这么大吧。有几个问题有点不太清楚。

1、预放大采样信号被采至CK2的NMOS开关导通电阻两端,导通电阻既不能太大(否则负阻超过正阻,直接导致采样时就latch了),也不能太小(否则预放大增益太小,增加亚稳态概率)。

1、Input stage和Flip flop之间没有开关,在正反馈过程中(即CK2=0),会不会继续受到输入信号的影响而导致比错。特别是在输入极接近,latch刚开始翻转的初始的一段时间。

2、Reset时(即CK2=1),Flipflop是四个NMOS二极管相接,输出在中间电平,会不会导致此时SR latch输出有误。

谢谢!又看了一下需要实现的ADC,比较器的共模输入范围只需0至Vref/2就足够了,是吧?还有,在复位(CLK2=1)时,CLK1是不应该为0,这样SR锁存器是处于锁存状态的,不会误触发吧。CLK1和CLK2的脉宽和周期对比较器的功能影响大不大,这两个时钟信号该如何考虑啊?

请问小编,你做的这个12bit sar的采样率大概多少呢?最近也在搞12bit的sar