LDO带周期变化电流负载的振荡问题

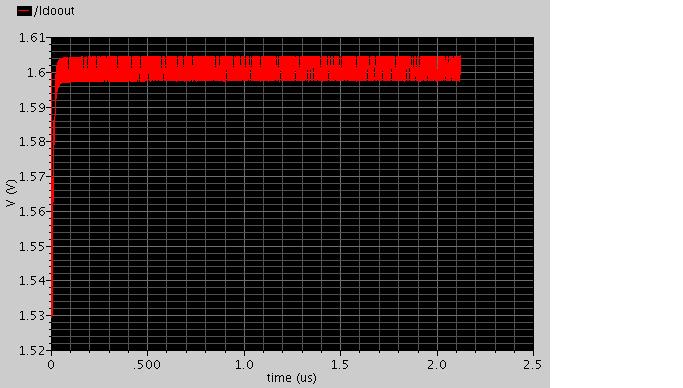

LDO带上VCO以后的仿真波形

Re

你所述分析是正确的,除了增加你ldo的带宽(功耗代价极大,不可取)外,增加输出电容是最好的办法。因为2.4Ghz的纹波,绝对不是ldo环路不稳定造成,而仅仅是高频负载的瞬态交流负载对电容的冲放电引起。

纹波大不是问题,导致vco的输出相位噪声差应该有两个因素:一个是LDO输出的噪声,另一个是VCO的压控增益,这两个结合导致的噪声差。降低kv,或者用超大电容在ldo输出滤除噪声,就应该不会恶化这么多了,你可以试试

谢谢我这个是全集成capacitor-less LDO,它的特点是输出没有大电容。因此还得想其他的办法。

LDO本身的输出噪声不会对VCO产生很大的影响,SCI有人证明在0.2DB以内。虽然我这个是全集成capacitor-less LDO, 我还是加了输出大电容做了尝试,在保持裕度的前提下,phase noise同样下降了20DB

输出电容多大?esr多大?

呵呵 前面不是说了

是capacitor-lessLDO没有输出电容和ESR

如果诚如你所说的,加LDO仿真VCO比单仿VCO相噪恶化20dB,那么看一下噪声贡献是不是主要来自于LDO?

如果是,那就表明是LDO引入的噪声,通过交叉耦合管源极到输出波形的AM-PM转换所致,如果LDO输出噪声很低,那你的AM-PM转换增益就很大,否则就是LDO噪声本身就很大,总之是两者共同作用导致的。

如果LDO噪声占输出主导,你可以仿真LDO输出到VCO输出的AM-PM转换增益,然后乘以LDO自己的输出噪声,就会得到输出的相噪值

非常感谢正是焦头烂额的时候。

我想请教你所说的:仿真LDO输出到VCO输出的AM-PM转换增益,然后乘以LDO自己的输出噪声,就会得到输出的相噪值

怎么进行这个仿真---怎么搭建接线,用什么仿真,怎么设置仿真

& Q! w, j2 I5 {+ mg9 g% N2 d`. o- Uj6 |. R+ D

你好 在LDO VCO联合系统里面,我通过noise仿真【设置input noise为LDO供电电源,output noise为vco的输出】,查看noise summary,发现排在前面的大部分的噪声都来自

LDO。这是否就是恶化VCO噪声的原因呢?

可是我看SCI上说LDO对phase noise的影响小于0.2DBC/HZ 几乎可以忽略不计。

另外 通过pss pnoise仿真也可以查看noise summary,这和上面的noise summary 有很大差别,但是表明主要的贡献还是来自LDO内部的管子。

应该怎么处理呢?

这种LDO用在VCO中合适吗?你说的恶化噪声主要是在频偏多大范围呢?VCO的LDO必须做成Low Noise,所以它的功耗以及尺寸都不能太小。对于LDO来说,它的输出噪声直接加在了VCO的电流源上,所以它对VCO的噪声影响类似尾电流源对VCO的噪声影响,所以flicker noise和二次谐波附近的噪声都会恶化VCO的相噪声。

所以首先要减小LDO的噪声,一般VCO的LDO中都有大电容滤掉噪声,然后减小VCO的Kvco值,以减小LDO的flicker noise影响。

你在LDO的输出加了大电容,仿真相噪还是没有改善,这个说不过去啊?

另外你的LDO的输出噪声做到多少呢?

我估计是LDO中flicker noise的影响。

嗯,flicker noise很难滤除,会通过AM-PM上变频到载波附近形成close-in phase noise

可以试着把大电容继续加大,看看大到多少相噪才会有改善?

正解。对于同样的kv,AM-PM的增益会随着频率的升高而增大,比如对于50MHz/v的kv,频率在2.4GHz,你的ldo的noise要在-155dB以下,噪底要在-170以下,否则我估计会在整个offset内都对vco噪声有很大影响。

当然,你可以用很大的电容滤波,要超大的,比如1000uF,这会滤除ldo输出noise在-200dB以下,但是AM-PM增益不会变。只是噪声下去了,贡献自然就下去了

非常感谢genny 和kool rfic08我回头再调试调试,再来汇报 请你们指点

单独仿真LDO的输出噪声是38 u V rms @22---22Khz 最大量的贡献来自MOS管。 我加大MOS WL值,这一噪声明显下降,不过带上vco后,phase noise也没有什么提高。

单独仿真LDO的输出噪声是 100.89 u V rms @10---1Mhz 最大量的贡献来自60K 100K 的两个LDO电阻,这一电阻就不好改变了。

AM-PM

对于低噪声的LDO设计,大家觉得设计最关键的是什么?怎么降低噪声?

另外 如果设计好了低噪声LDO ,真的能否解决前面的那个20DBC/HZ的phase noise差距吗?

低噪声而且高PSR的LDO

好的,学习学习

学习了

你的bandgap噪声够低么?

always a good topic for us to study more !

呵呵 也出现了你说的问题第一 确保你的bandgap是低噪声的 如果你的bandgap不是低噪的话 在其输出加大电容 或许要在片外加形成低通滤波第二 你看了noise summary 发现时ldo的问题那么务必增加EA第一级宽长积 可以减小1/f噪声第二 增大第一级输入管的gm(减小其过驱动电压,减到100mv) 减小第一级负载管的gm (减小其宽长比) 第三 从你表述上看fb res 在1M频偏 映入了噪声比较多 那就适量减小一些 但是会增大静态电流如果效果还是不明显 那就做成两级ldo的形式 将fb res 移到第一级ldo的输出这样第二级ldo可以接成单位增益的形式(不需要fb res)

学习学习。

学习学习

maybe also the error amplifier needs to be low noise.