做CDR的大神们看过来

时间:10-02

整理:3721RD

点击:

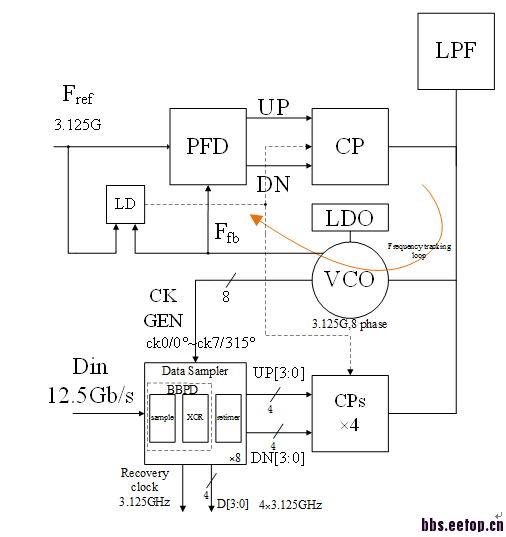

我在做一个双环路的CDR,锁频环路和锁相环路共用一个VCO,当输入数据为周期方波时,可以正常工作,如下图

而输入为NRZ码时,锁相时会出现问题,如下图

其中一个是锁定信号,一个是VCO的控制电压,可以看出,当输入为NRZ码时,锁相环路工作时控制电压会下降,导致失锁。

这是为什么呢?

而输入为NRZ码时,锁相时会出现问题,如下图

其中一个是锁定信号,一个是VCO的控制电压,可以看出,当输入为NRZ码时,锁相环路工作时控制电压会下降,导致失锁。

这是为什么呢?

电路结构是什么样子的

自己顶,不能沉

是不是LD的阈值设置的太小?

好像是loop 不稳定

不是啊这不是调节过程中产生的正常波动,而是锁相环路最终稳定时的电压就不对,锁定到了别的频率,不是LD的阈值问题吧

我认为这种两个环路共用VCO的结构本身就有缺陷,你说的loop不稳定能具体说一下嘛?